Cypress enCoRe CY7C602xx User Manual

Encore™ ii low voltage microcontroller, Features, Logic block diagram

CY7C601xx, CY7C602xx

enCoRe™ II Low Voltage Microcontroller

Cypress Semiconductor Corporation

•

198 Champion Court

•

San Jose

,

CA 95134-1709

•

408-943-2600

Document 38-16016 Rev. *E

Revised December 08, 2008

1. Features

■

enCoRe

™ II Low Voltage (enCoRe II LV)—enhanced

component reduction

❐

Internal crystalless oscillator with support for optional exter-

nal clock or external crystal or resonator

❐

Configurable IO for real world interface without external com-

ponents

■

Enhanced 8-bit microcontroller

❐

Harvard architecture

❐

M8C CPU speed up to 12 MHz or sourced by an external

crystal, resonator, or clock signal

■

Internal memory

❐

256 bytes of RAM

❐

8 Kbytes of Flash including EEROM emulation

■

Low power consumption

❐

Typically 2.25 mA at 3 MHz

❐

5

μA sleep

■

In-system reprogrammability

❐

Allows easy firmware update

■

General purpose IO ports

❐

Up to 36 General Purpose IO (GPIO) pins

❐

2 mA source current on all GPIO pins. Configurable 8 or

50 mA per pin current sink on designated pins

❐

Each GPIO port supports high impedance inputs, config-

urable pull up, open drain output, CMOS and TTL inputs, and

CMOS output

❐

Maskable interrupts on all IO pins

■

SPI serial communication

❐

Master or slave operation

❐

Configurable up to 2 Mbit per second transfers

❐

Supports half duplex single data line mode for optical sensors

■

2-channel 8-bit or 1-channel 16-bit capture timer registers.

Capture timer registers store both rising and falling edge times

❐

Two registers each for two input pins

❐

Separate registers for rising and falling edge capture

❐

Simplifies interface to RF inputs for wireless applications

■

Internal low power wakeup timer during suspend mode

❐

Periodic wakeup with no external components

■

Programmable interval timer interrupts

■

Reduced RF emissions at 27 MHz and 96 MHz

■

Watchdog timer (WDT)

■

Low voltage detection with user selectable threshold voltages

■

Improved output drivers to reduce EMI

■

Operating voltage from 2.7V to 3.6V DC

■

Operating temperature from 0–70°C

■

Available in 24 and 40-pin PDIP, 24-pin SOIC, 24-pin QSOP

and SSOP, 28-pin SSOP, and 48-pin SSOP

■

Advanced development tools based on Cypress PSoC

®

tools

■

Industry standard programmer support

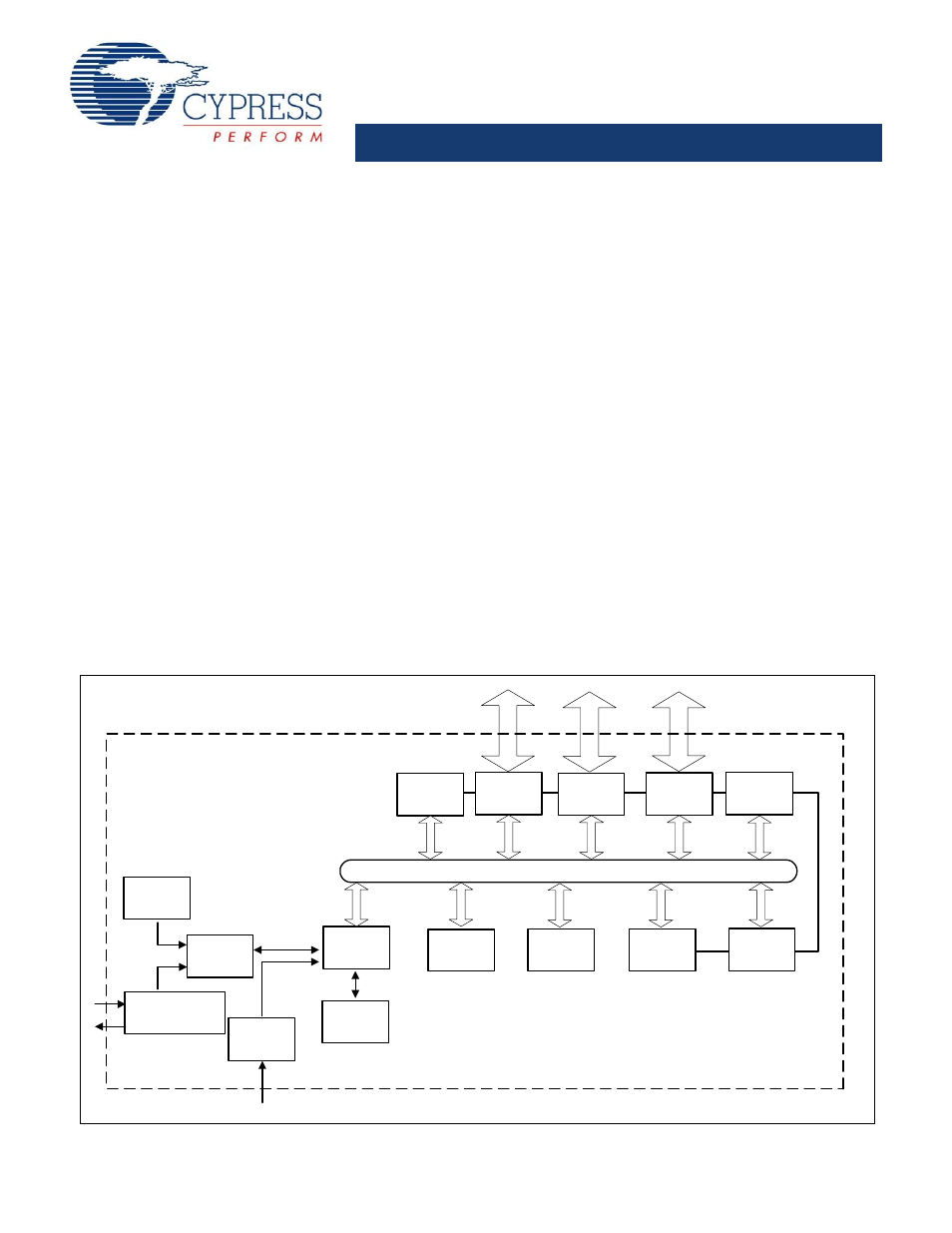

Internal

12 MHz

Oscillator

Clock

Control

Crystal

Oscillator

CY7C601xx only

POR /

Low-Voltage

Detect

Watchdog

Timer

M8C CPU

16 Extended

I/O Pins

16 GPIO

Pins

Wakeup

Timer

Capture

Timers

12-bit Timer

Vd

d

Interrupt

Control

4 SPI/GPIO

Pins

Flash

8K Byte

RAM

256 Byte

2. Logic Block Diagram

Document Outline

- 1. Features

- 2. Logic Block Diagram

- 3. Applications

- 4. Introduction

- 5. Conventions

- 6. Pinouts

- 7. Register Summary

- 8. CPU Architecture

- 9. CPU Registers

- 9.1 Flags Register

- 9.2 Addressing Modes

- 9.2.1 Source Immediate

- 9.2.2 Source Direct

- 9.2.3 Source Indexed

- 9.2.4 Destination Direct

- 9.2.5 Destination Indexed

- 9.2.6 Destination Direct Source Immediate

- 9.2.7 Destination Indexed Source Immediate

- 9.2.8 Destination Direct Source Direct

- 9.2.9 Source Indirect Post Increment

- 9.2.10 Destination Indirect Post Increment

- 10. Instruction Set Summary

- 11. Memory Organization

- 12. Clocking

- 13. Reset

- 14. Sleep Mode

- 15. Low Voltage Detect Control

- 16. General Purpose IO Ports

- 16.1 Port Data Registers

- 16.2 GPIO Port Configuration

- 16.2.1 Int Enable

- 16.2.2 Int Act Low

- 16.2.3 TTL Thresh

- 16.2.4 High Sink

- 16.2.5 Open Drain

- 16.2.6 Pull Up Enable

- 16.2.7 Output Enable

- 16.2.8 SPI Use

- 16.2.9 P0.0/CLKIN Configuration

- 16.2.10 P0.1/CLKOUT Configuration

- 16.2.11 P0.2/INT0-P0.4/INT2 Configuration

- 16.2.12 P0.5/TIO0-P0.6/TIO1 Configuration

- 16.2.13 P0.7 Configuration

- 16.2.14 P1.0 Configuration

- 16.2.15 P1.1 Configuration

- 16.2.16 P1.2 Configuration

- 16.2.17 P1.3 Configuration (SSEL)

- 16.2.18 P1.4-P1.6 Configuration (SCLK, SMOSI, SMISO)

- 16.2.19 P1.7 Configuration

- 16.2.20 P2 Configuration

- 16.2.21 P3 Configuration

- 16.2.22 P4 Configuration

- 17. Serial Peripheral Interface (SPI)

- 18. Timer Registers

- 19. Interrupt Controller

- 20. Absolute Maximum Ratings

- 21. Ordering Information

- 22. Package Handling

- 23. Package Diagrams

- 24. Document History Page

- Sales, Solutions, and Legal Information