Address bus connections – Digilent 410-044-10P-KIT User Manual

Page 12

12

Spartan-3 Starter Kit Board User Guide

1-800-255-7778

UG130 (v1.1) May 13, 2005

Chapter 2: Fast, Asynchronous SRAM

R

The SRAM array forms either a single 256Kx32 SRAM memory or two independent

256Kx16 arrays. Both SRAM devices share common write-enable (WE#), output-enable

(OE#), and address (A[17:0]) signals. However, each device has a separate chip select

enable (CE#) control and individual byte-enable controls to select the high or low byte in

the 16-bit data word, UB and LB, respectively.

The 256Kx32 configuration is ideally suited to hold MicroBlaze instructions. However, it

alternately provides high-density data storage for a variety of applications, such as digital

signal processing (DSP), large data FIFOs, and graphics buffers.

Address Bus Connections

Both 256Kx16 SRAMs share 18-bit address control lines, as shown in

Table 2-1

. These

address signals also connect to the A1 Expansion Connector (see

).

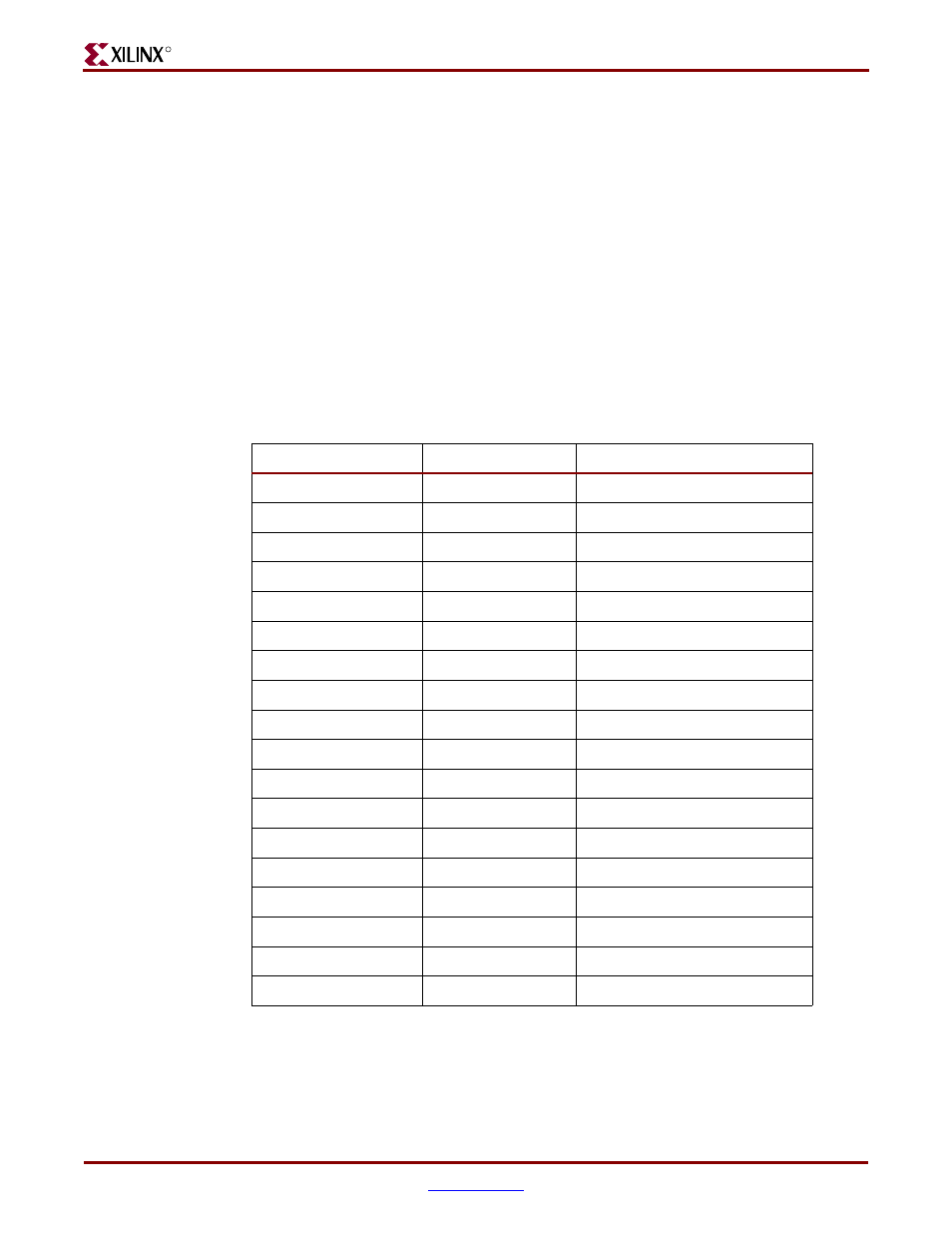

Table 2-1:

External SRAM Address Bus Connections to Spartan-3 FPGA

Address Bit

FPGA Pin

A1 Expansion Connector Pin

A17

L3

35

A16

K5

33

A15

K3

34

A14

J3

31

A13

J4

32

A12

H4

29

A11

H3

30

A10

G5

27

A9

E4

28

A8

E3

25

A7

F4

26

A6

F3

23

A5

G4

24

A4

L4

14

A3

M3

12

A2

M4

10

A1

N3

8

A0

L5

6