Digilent DIO2 User Manual

Page 16

Digilab DIO2 Reference Manual

Digilent, Inc.

www.digilentinc.com

page 16 of 19

Copyright Digilent, Inc. All rights reserved. Other product and company names mentioned may be trademarks of their respective owners.

Memory map

The memory map implemented in the CPLD bus controller is shown below. Note that all six address

lines are decoded in write mode, but only the two least-significant address bits are decoded for read

mode (so the same four locations will alias through the entire read address space).

Self test mode

A self-test mode has been included in the CPLD configuration to allow a quick check of DIO2 board

function. The self test mode enable signal can be asserted by setting SW1 to output VDD, SW8 to

output GND, and holding down BTNE and BTN7. Self test mode can be activated by pressing BTN0

while the test mode enable signal is asserted, and deactivated by pressing BTN0 while the test mode

enable signal is not asserted. When in test mode, the buttons drive the individual LEDs, and the

switches drive the seven-segment displays.

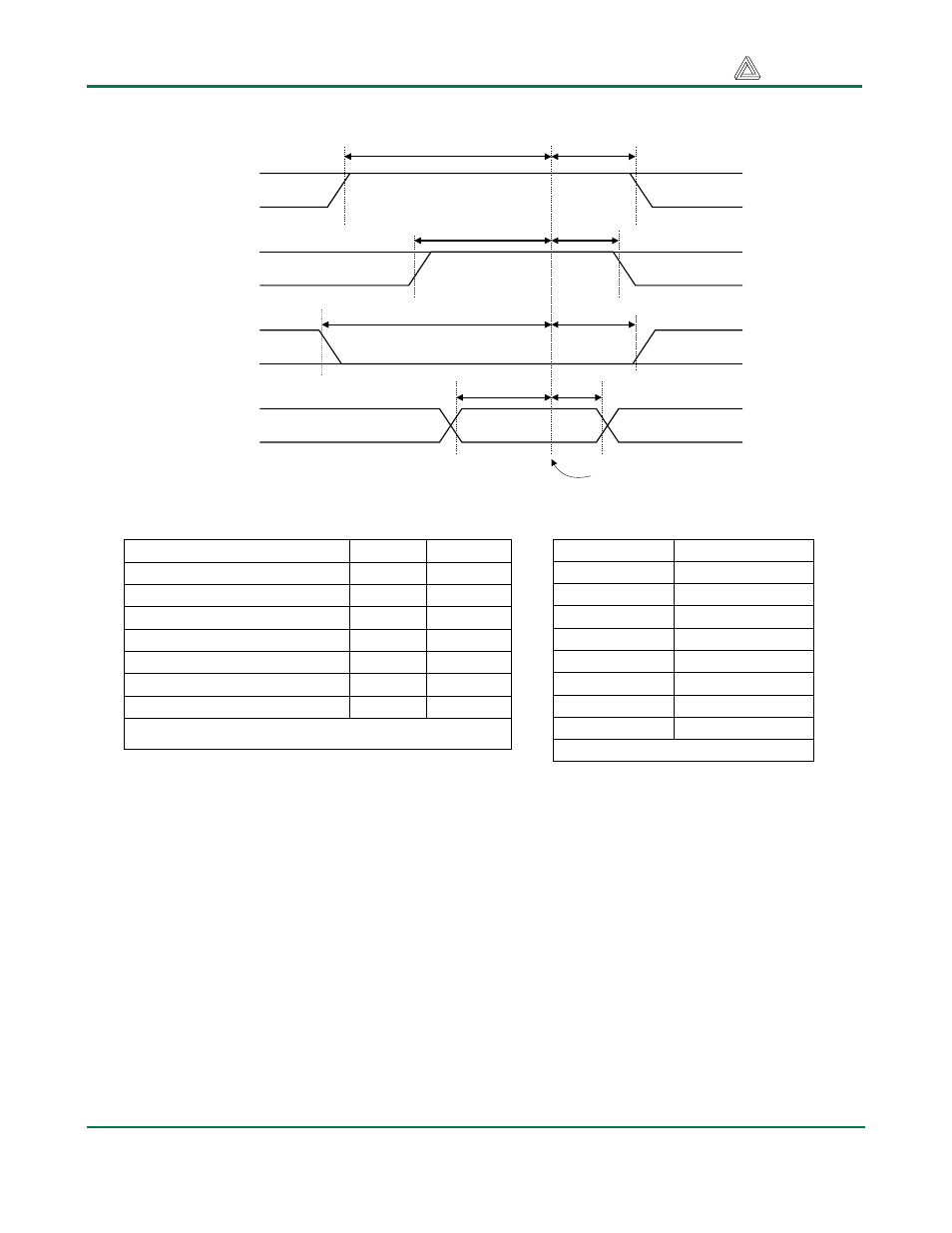

twd

th

OE

CS

WE

DB0-DB7

th

teoe

tsu

tdoe

tw

Read data latch time

th

Parameter Symbol

Min(ns)

Write cycle time

tw

15

Write strobe hold time

th

2

OE output disable time

tdoe

10

OE output enable time

tsu

10

Data setup time

tsu

7

Data hold time

th

0

Write strobe disable time

twd

10

CPLD-System board bus timings

Address 0

Buttons 7 - 0

Address 1

Buttons 14 - 8

Address 2

Switches 8 - 1

Address 3

Not Used

Address 4

LEDs 7 - 0

Address 5

LEDs F - 8

Address 6

7S digits 1 & 2

Address 7

7S digits 3 & 4

Address 8-63 Not Used

CPLD Address Map