Pll and clocking, Dc-to-dc converter interface (pwm), Timers – Cirrus Logic EP7309 User Manual

Page 9: General purpose input/output (gpio), Hardware debug interface, Led flasher

DS507F2

Copyright Cirrus Logic, Inc. 2011

(All Rights Reserved)

9

EP7309

High-Performance, Low-Power System on Chip

PLL and Clocking

•

Processor and Peripheral Clocks operate from a single

3.6864 MHz crystal or external 13 MHz clock

•

Programmable clock speeds allow the peripheral bus to run

at 18 MHz when the processor is set to 18 MHz and at

36 MHz when the processor is set to 36, 49 or 74 MHz

DC-to-DC converter interface (PWM)

•

Provides two 96 kHz clock outputs with programmable

duty ratio (from 1-in-16 to 15-in-16) that can be used to

drive a positive or negative DC to DC converter

Timers

•

Internal (RTC) timer

•

Two internal 16-bit programmable hardware count-down

timers

General Purpose Input/Output (GPIO)

•

Three 8-bit and one 3-bit GPIO ports

•

Supports scanning keyboard matrix

Note:

Pins are multiplexed. See

for

more information.

Hardware debug Interface

•

Full JTAG boundary scan and Embedded ICE

support

LED Flasher

A dedicated LED flasher module can be used to generate a low

frequency signal on Port D pin 0 for the purpose of blinking an

LED without CPU intervention. The LED flasher feature is

ideal as a visual annunciator in battery powered applications,

such as a voice mail indicator on a portable phone or an

appointment reminder on a PDA.

•

Software adjustable flash period and duty cycle

•

Operates from 32 kHz RTC clock

•

Will continue to flash in IDLE and STANDBY states

•

4 mA drive current

Note:

Pins are multiplexed. See

for

more information.

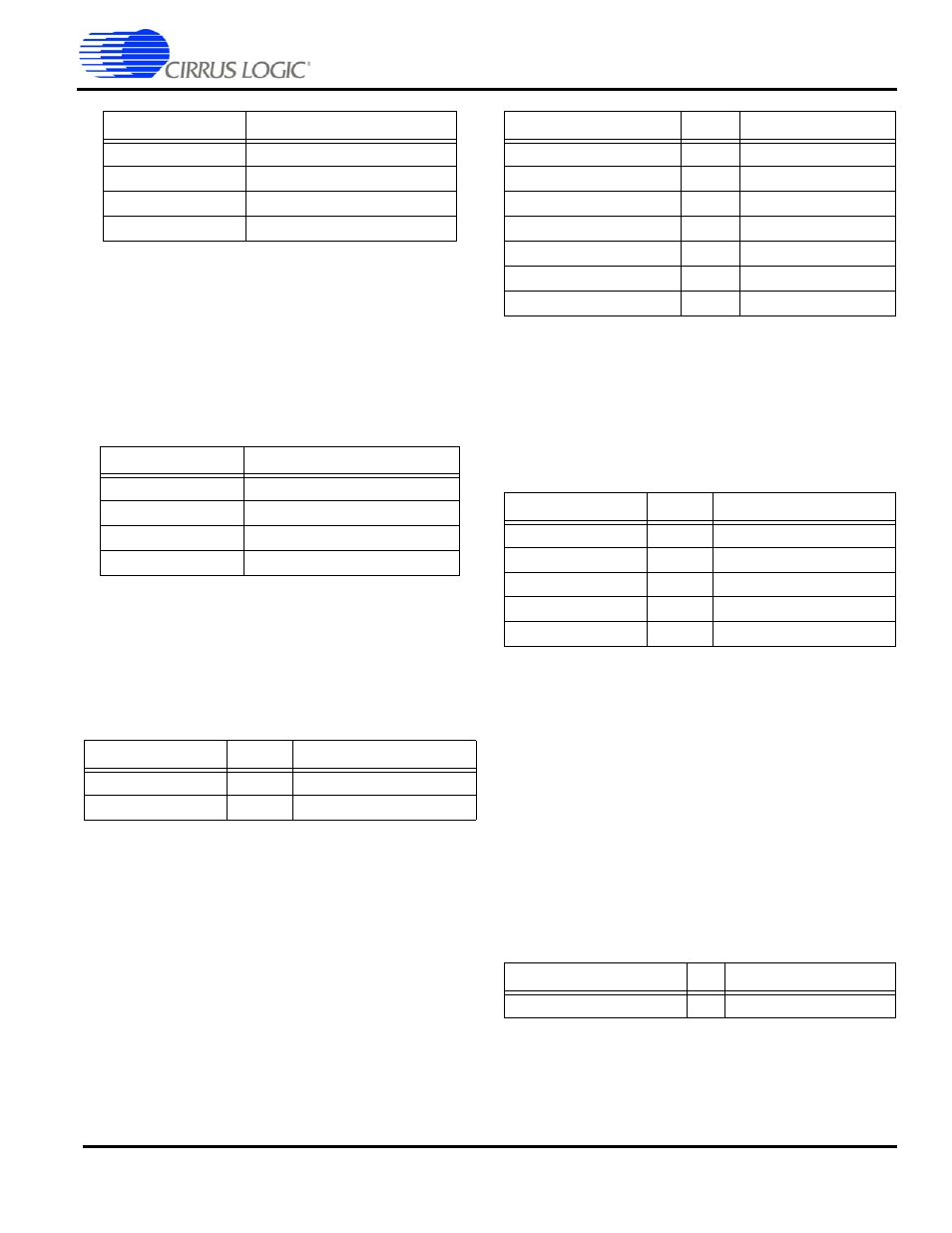

Pin Mnemonic

Pin Description

RTCIN

Real-Time Clock Oscillator Input

RTCOUT

Real-Time Clock Oscillator Output

VDDRTC

Real-Time Clock Oscillator Power

VSSRTC

Real-Time Clock Oscillator Ground

Table 11. Real-Time Clock Pin Assignments

Pin Mnemonic

Pin Description

MOSCIN

Main Oscillator Input

MOSCOUT

Main Oscillator Output

VDDOSC

Main Oscillator Power

VSSOSC

Main Oscillator Ground

Table 12. PLL and Clocking Pin Assignments

Pin Mnemonic

I/O

Pin Description

DRIVE[1:0]

I/O

PWM drive output

FB[1:0]

I

PWM feedback input

Table 13. DC-to-DC Converter Interface Pin Assignments

Pin Mnemonic

I/O

Pin Description

PA[7:0]

I/O

GPIO port A

PB[7:0]

I/O

GPIO port B

PD[0]/LEDFLSH

(Note)

I/O

GPIO port D

PD[5:1]

I/O

GPIO port D

PD[7:6]/SDQM[1:0]

(Note)

I/O

GPIO port D

PE[1:0]/BOOTSEL[1:0] (Note)

I/O

GPIO port E

PE[2]/CLKSEL

(Note)

I/O

GPIO port E

Table 14. General Purpose Input/Output Pin Assignments

Pin Mnemonic

I/O

Pin Description

TCLK

I

JTAG clock

TDI

I

JTAG data input

TDO

O

JTAG data output

nTRST

I

JTAG async reset input

TMS

I

JTAG mode select

Table 15. Hardware Debug Interface Pin Assignments

Pin Mnemonic

I/O

Pin Description

PD[0]/LEDFLSH

(Note)

O

LED flasher driver

Table 16. LED Flasher Pin Assignments