Cirrus Logic EP7309 User Manual

Page 28

28

Copyright Cirrus Logic, Inc. 2011

(All Rights Reserved)

DS507F2

EP7309

High-Performance, Low-Power System on Chip

*With p/u’ means with internal pull-up on the pin.

148

A[7]

O

1

Low

149

VSSIO

Pad Gnd

150

D[7]

I/O

1

Low

151

nBATCHG

I

152

nEXTPWR

I

153

BATOK

I

154

nPOR

I

Schmitt

155

nMEDCHG/

nBROM

I

156

nURESET

I

Schmitt

157

VDDOSC

Osc Pwr

158

MOSCIN

Osc

159

MOSCOUT

Osc

160

VSSOSC

Osc Gnd

161

WAKEUP

I

Schmitt

162

nPWRFL

I

163

A[6]

O

1

Low

164

D[6]

I/O

1

Low

165

A[5]

Out

1

Low

166

D[5]

I/O

1

Low

167

VDDIO

Pad Pwr

168

VSSIO

Pad Gnd

169

A[4]

O

1

Low

170

D[4]

I/O

1

Low

171

A[3]

O

2

Low

172

D[3]

I/O

1

Low

173

A[2]

O

2

Low

174

VSSIO

Pad Gnd

175

D[2]

I/O

1

Low

176

A[1]

O

2

Low

177

D[1]

I/O

1

Low

178

A[0]

O

2

Low

179

D[0]

I/O

1

Low

180

VSS CORE

Core Gnd

181

VDD CORE

Core Pwr

182

VSSIO

Pad Gnd

183

VDDIO

Pad Pwr

184

CL[2]

O

1

Low

185

CL[1]

O

1

Low

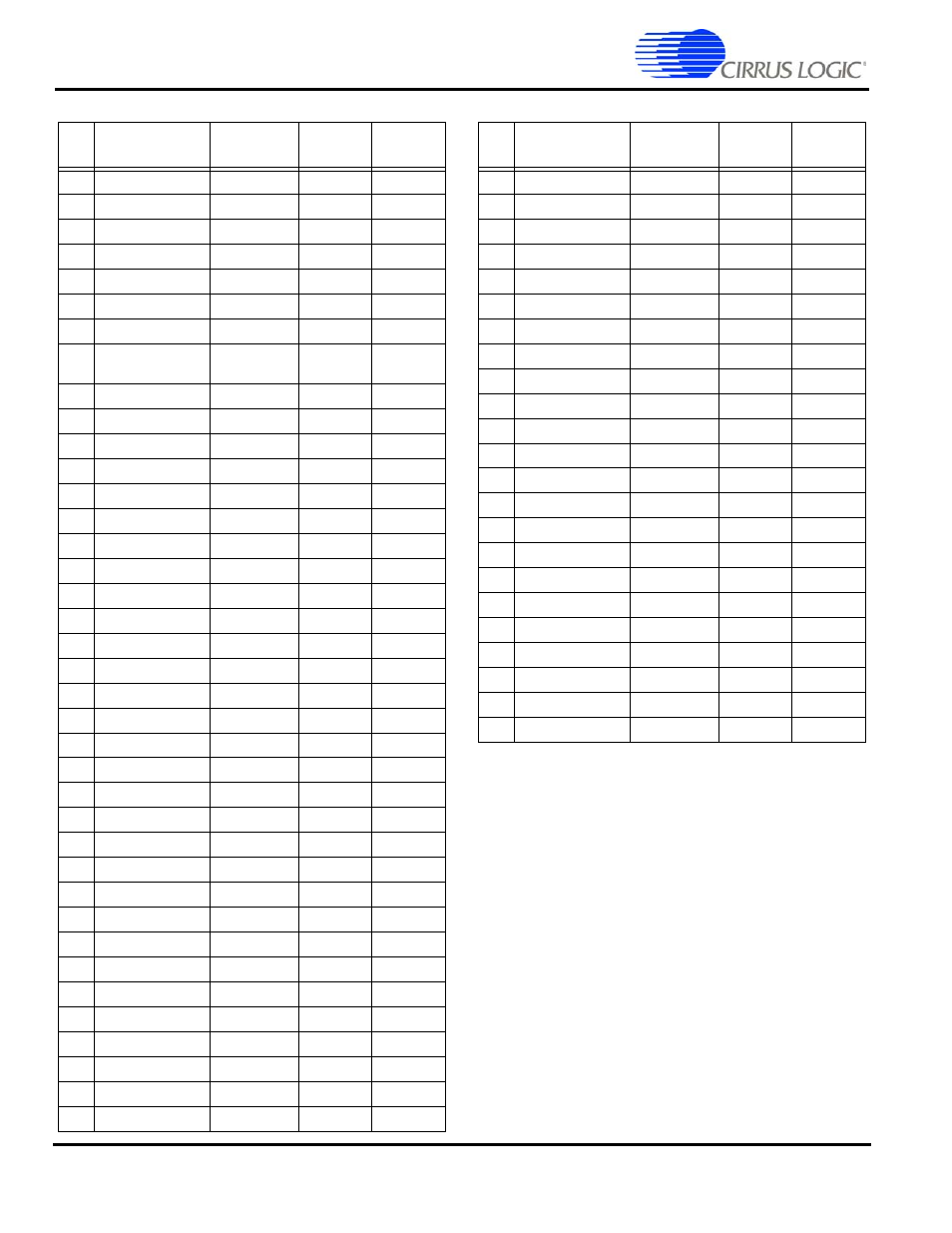

Table 19. 208-Pin LQFP Numeric Pin Listing (Continued)

Pin

No.

Signal

Type

Strength

Reset

State

186

FRM

O

1

Low

187

M

O

1

Low

188

DD[3]

I/O

1

Low

189

DD[2]

I/O

1

Low

190

VSSIO

Pad Gnd

191

DD[1]

I/O

1

Low

192

DD[0]

I/O

1

Low

193

N/C

O

1

High

194

N/C

O

1

High

195

N/C

I/O

2

Low

196

N/C

I/O

2

Low

197

VDDIO

Pad Pwr

198

VSSIO

Pad Gnd

199

N/C

I/O

2

Low

200

N/C

I/O

2

Low

201

nMWE

O

1

High

202

nMOE

O

1

High

203

VSSIO

Pad Gnd

204

nCS[0]

O

1

High

205

nCS[1]

O

1

High

206

nCS[2]

O

1

High

207

nCS[3]

O

1

High

208

nCS[4]

O

1

High

Table 19. 208-Pin LQFP Numeric Pin Listing (Continued)

Pin

No.

Signal

Type

Strength

Reset

State