Cirrus Logic EP7309 User Manual

Page 37

DS507F2

Copyright Cirrus Logic, Inc. 2011

(All Rights Reserved)

37

EP7309

High-Performance, Low-Power System on Chip

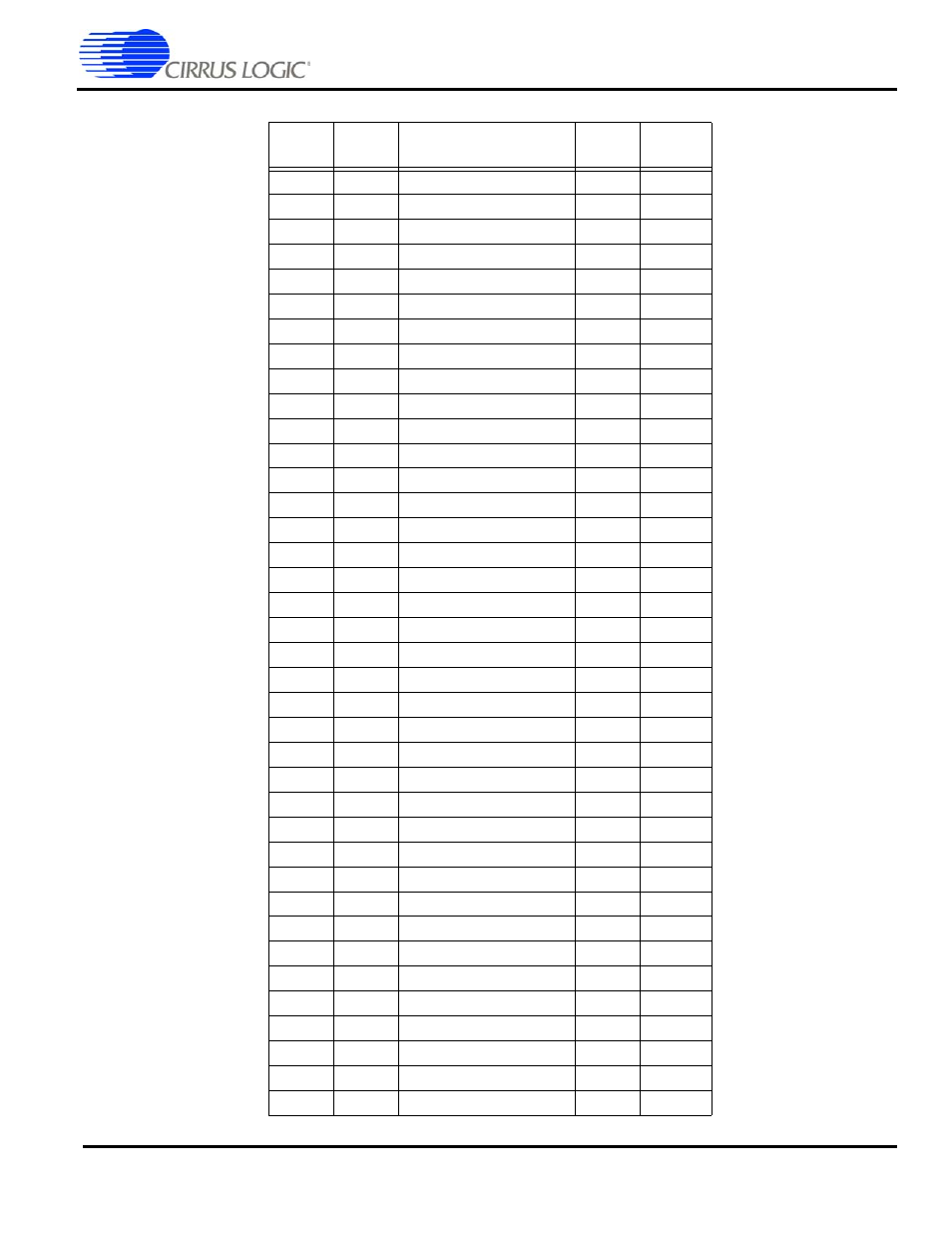

148

G11

A[7]

O

274

150

D15

D[7]

I/O

276

151

F13

nBATCHG

I

279

152

C16

nEXTPWR

I

280

153

F12

BATOK

I

281

154

C15

nPOR

I

282

155

E13

nMEDCHG/nBROM

I

283

156

B16

nURESET

I

284

161

B14

WAKEUP

I

285

162

D11

nPWRFL

I

286

163

A13

A[6]

O

287

164

F10

D[6]

I/O

289

165

B13

A[5]

O

292

166

E10

D[5]

I/O

294

169

B12

A[4]

O

297

170

D10

D[4]

I/O

299

171

A11

A[3]

O

302

172

G9

D[3]

I/O

304

173

B11

A[2]

O

307

175

A10

D[2]

I/O

309

176

F9

A[1]

O

312

177

B10

D[1]

I/O

314

178

E9

A[0]

O

317

179

A9

D[0]

I/O

319

184

D8

CL2

O

322

185

B8

CL1

O

324

186

E8

FRM

O

326

187

A7

M

O

328

188

F8

DD[3]

I/O

330

189

B7

DD[2]

I/O

333

191

A6

DD[1]

I/O

336

192

G8

DD[0]

I/O

339

193

B6

N/C

O

342

194

D7

N/C

O

344

195

A5

N/C

I/O

346

196

E7

N/C

I/O

349

199

F7

N/C

I/O

352

200

A4

N/C

I/O

355

Table 21. JTAG Boundary Scan Signal Ordering (Continued)

LQFP

Pin No.

PBGA

Ball

Signal

Type

Position

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1501 (16 pages)

- CS1601 (2 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)

- CS2000-CP (38 pages)