Processor core - arm720t, Power management, Maverickkey™ unique id – Cirrus Logic EP7309 User Manual

Page 6: Memory interfaces, Digital audio capability, Maverickkey, Unique id

6

Copyright Cirrus Logic, Inc. 2011

(All Rights Reserved)

DS507F2

EP7309

High-Performance, Low-Power System on Chip

Processor Core - ARM720T

The EP7309 incorporates an ARM 32-bit RISC

microcontroller that controls a wide range of on-chip

peripherals. The processor utilizes a three-stage pipeline

consisting of fetch, decode and execute stages. Key features

include:

•

ARM (32-bit) and Thumb (16-bit compressed) instruction

sets

•

Enhanced MMU for Microsoft Windows CE and other

operating systems

•

8 KB of 4-way set-associative cache.

•

Translation Look Aside Buffers with 64 Translated Entries

Power Management

The EP7309 is designed for ultra-low-power operation. Its core

operates at only 2.5 V, while its I/O has an operation range of

2.5 V–3.3 V allowing the device to achieve a performance

level equivalent to 60 MIPS. The device has three basic power

states:

• Operating — This state is the full performance state.

All the clocks and peripheral logic are enabled.

• Idle — This state is the same as the Operating State,

except the CPU clock is halted while waiting for an

event such as a key press.

• Standby — This state is equivalent to the computer

being switched off (no display), and the main

oscillator shut down. An event such as a key press

can wake-up the processor.

MaverickKey

™

Unique ID

MaverickKey unique hardware programmed IDs are a solution

to the growing concern over secure web content and

commerce. With Internet security playing an important role in

the delivery of digital media such as books or music,

traditional software methods are quickly becoming unreliable.

The MaverickKey unique IDs provide OEMs with a method of

utilizing specific hardware IDs such as those assigned for

SDMI (Secure Digital Music Initiative) or any other

authentication mechanism.

Both a specific 32-bit ID as well as a 128-bit random ID is

programmed into the EP7309 through the use of laser probing

technology. These IDs can then be used to match secure

copyrighted content with the ID of the target device the

EP7309 is powering, and then deliver the copyrighted

information over a secure connection. In addition, secure

transactions can benefit by also matching device IDs to server

IDs. MaverickKey IDs provide a level of hardware security

required for today’s Internet appliances.

Memory Interfaces

The EP7309 is equiped with a ROM/SRAM/FLASH-style

interface that has programmable wait-state timings and

includes burst-mode capability, with six chip selects decoding

six 256 MB sections of addressable space. For maximum

flexibility, each bank can be specified to be 8-, 16-, or 32-bits

wide. This allows the use of 8-bit-wide boot ROM options to

minimize overall system cost. The on-chip boot ROM can be

used in product manufacturing to serially download system

code into system FLASH memory. To further minimize system

memory requirements and cost, the ARM Thumb instruction

set is supported, providing for the use of high-speed 32-bit

operations in 16-bit op-codes and yielding industry-leading

code density.

Digital Audio Capability

The EP7309 uses its powerful 32-bit RISC processing engine

to implement audio decompression algorithms in software. The

nature of the on-board RISC processor, and the availability of

efficient C-compilers and other software development tools,

ensures that a wide range of audio decompression algorithms

can easily be ported to and run on the EP7309

Universal Asynchronous

Receiver/Transmitters (UARTs)

The EP7309 includes two 16550-type UARTs for RS-232

serial communications, both of which have two 16-byte FIFOs

for receiving and transmitting data. The UARTs support bit

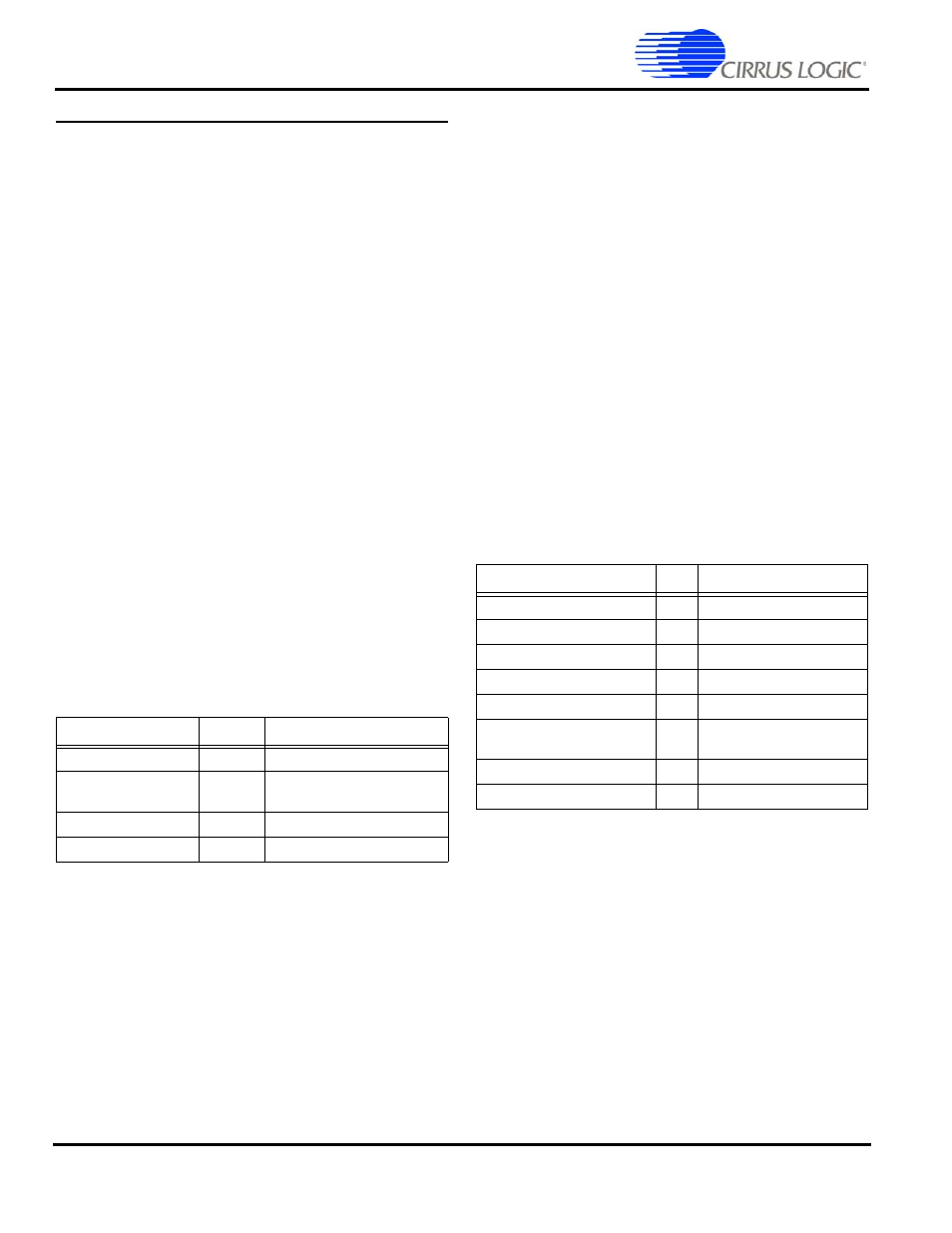

Pin Mnemonic

I/O

Pin Description

BATOK

I

Battery ok input

nEXTPWR

I

External power supply sense

input

nPWRFL

I

Power fail sense input

nBATCHG

I

Battery changed sense input

Table 1. Power Management Pin Assignments

Pin Mnemonic

I/O

Pin Description

nCS[5:0]

O

Chip select out

A[27:0]

O

Address output

D[31:0]

I/O

Data I/O

nMOE

O

ROM expansion OP enable

nMWE

O

ROM expansion write enable

HALFWORD

O

Halfword access select

output

WORD

O

Word access select output

WRITE

O

Transfer direction

Table 2. Static Memory Interface Pin Assignments