Cirrus Logic EP7309 User Manual

Page 35

DS507F2

Copyright Cirrus Logic, Inc. 2011

(All Rights Reserved)

35

EP7309

High-Performance, Low-Power System on Chip

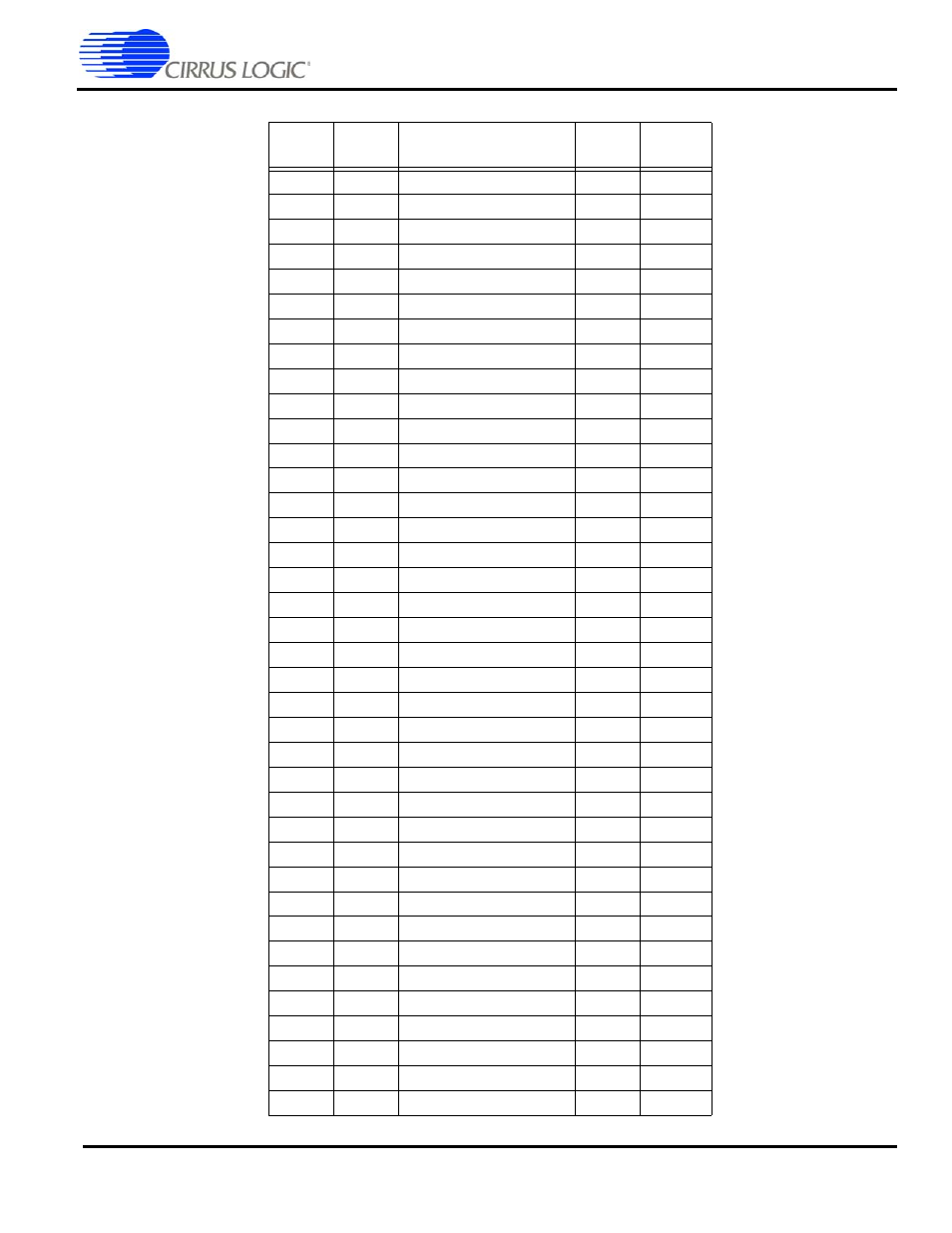

44

N1

nEXTFIQ

I

79

45

L5

PE[2]/CLKSEL

I/O

80

46

N2

PE[1]/BOOTSEL1

I/O

83

47

M4

PE[0]/BOOTSEL0

I/O

86

53

T2

PD[7]

I/O

89

54

T3

PD[6]

I/O

92

55

N5

PD[5]

I/O

95

56

R3

PD[4]

I/O

98

59

T4

PD[3]

I/O

101

60

N6

PD[2]

I/O

104

61

R4

PD[1]

I/O

107

62

L7

PD[0]/LEDFLSH

O

110

68

T6

SSIRXFR

I/O

122

69

K8

ADCIN

I

125

70

R6

nADCCS

O

126

75

M8

DRIVE1

I/O

128

76

T8

DRIVE0

I/O

131

77

N8

ADCCLK

O

134

78

R8

ADCOUT

O

136

79

N9

SMPCLK

O

138

80

T9

FB1

I

140

82

M9

FB0

I

141

83

R9

COL7

O

142

84

L9

COL6

O

144

85

T10

COL5

O

146

86

K9

COL4

O

148

87

R10

COL3

O

150

88

N10

COL2

O

152

91

R11

COL1

O

154

92

M10

COL0

O

156

93

T12

BUZ

O

158

94

L10

D[31]

I/O

160

95

R12

D[30]

I/O

163

96

N11

D[29]

I/O

166

97

T13

D[28]

I/O

169

99

R13

A[27]

Out

172

100

M11

D[27]

I/O

174

101

T14

A[26]

O

177

Table 21. JTAG Boundary Scan Signal Ordering (Continued)

LQFP

Pin No.

PBGA

Ball

Signal

Type

Position

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1501 (16 pages)

- CS1601 (2 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)

- CS2000-CP (38 pages)