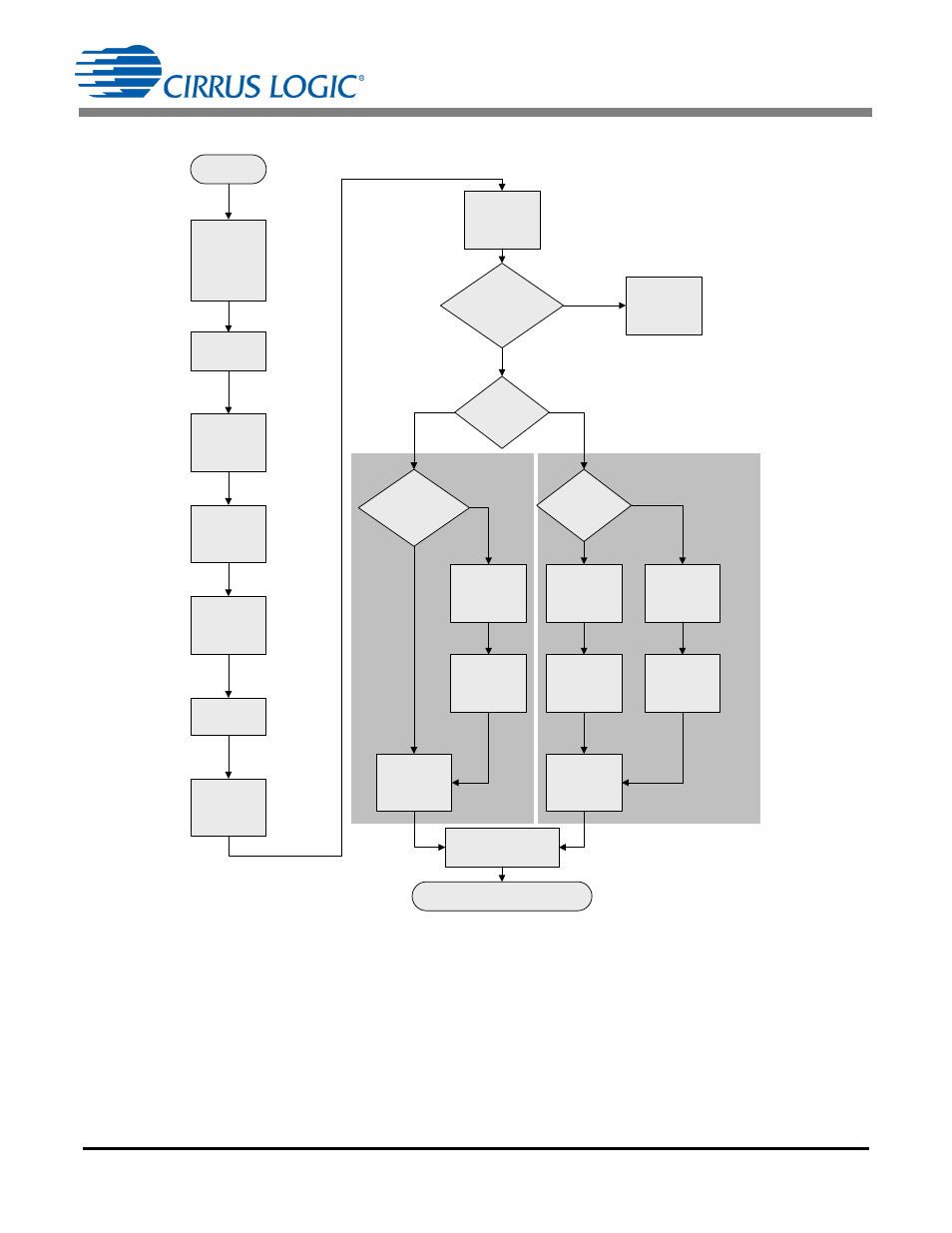

An366, Figure 9. phase compensation flow – Cirrus Logic AN366 User Manual

Page 16

AN366

16

AN366REV2

RESOLUTION

MULTIPLIER

0.008789 (50Hz)

(Note 1)

-8.99º <

PHASE OFFSET

< +8.99º (50Hz)

?

(Note 2)

PHASE OFFSET

NEGATIVE

?

FINE

COMPENSATION

(FPCC) = -PHASE

OFFSET ÷

0.008789 (50Hz)

0 <

PHASE OFFSET

< 512 · 0.008789

(50Hz)

?

FINE

COMPENSATION

(FPCC) = PHASE

OFFSET ÷

0.008789 (50Hz)

SET COARSE

COMPENSATION

(CPCC = 01)

1 OWR on I

PHASE OFFSET =

PHASE OFFSET +

4.5º (50Hz)

SET COARSE

COMPENSATION

(CPCC = 11)

2 OWR on V

PHASE OFFSET =

8.99º - PHASE

OFFSET (50Hz)

FAIL

METER

PHASE COMPENSATION COMPLETE

(RETURN CPCC & FPCC to MAIN)

ACCUMULATE MULTIPLE

PF READING AND

CONFIRM PF = 0.5

SET COARSE

COMPENSATION

(CPCC = 10)

1 OWR on V

PHASE OFFSET =

4.5º - PHASE

OFFSET

(50Hz)

±10.79º @ 60Hz

0.010547 @ 60Hz

0 to 512

0.010547 @ 60Hz

-512

0.010547 to 0 @ 60Hz

5.4º @ 60Hz

10.79º @ 60Hz

5.4º @ 60Hz

0.010547 @ 60Hz

NO

YES

NO

YES

NO

YES

NO

YES

-512 · 0.008789 <

PHASE OFFSET

< 0 (50Hz)

?

Note 4

Note 5

No coarse

comp.

CPCC=00

APPLY

REFERENCE

LINE VOLTAGE

AND

60

O

LAGGING

LOAD CURRENT

PF=0.5

START

CONTINUOUS

CONVERSION

0xD5

FROM MAIN

FLOW

READ PF

CALCULATE

PHASE

OFFSET =

arccos(PF)-60º

STOP

CONVERSIONS

0xD8

Tsettle =

2000 ms

(Note 1)

SampleCount

(N)= 16,000

(Note 1)

Figure 9. Phase Compensation Flow

Note 1:Larger numbers in the Tsettle and SampleCount registers will increase calibration precision.

Note 2: OWR=4000, MCLK=4.096Mhz.

Note 3: For an expanded view showing more information about the phase compensation flow, see Phase Compensation Flow Diagram

on page 40.

Note 4: Before calibration: Angle < 60; Phase offset < 0; I leads V; PF is leading--for more positive, delay I.

Note 5: Before calibration: Angle < 60; Phase offset < 0; I lags V; PF is lagging--only coarse adjustment can delay V, therefore delay

V by 1 or 2 OWR and delay I by less than 1 or 2 OWR.