Aduc812 – Analog Devices ADuC812 User Manual

Page 55

REV. B

ADuC812

–55–

Parameter

Min

Typ

Max

Unit

Figure

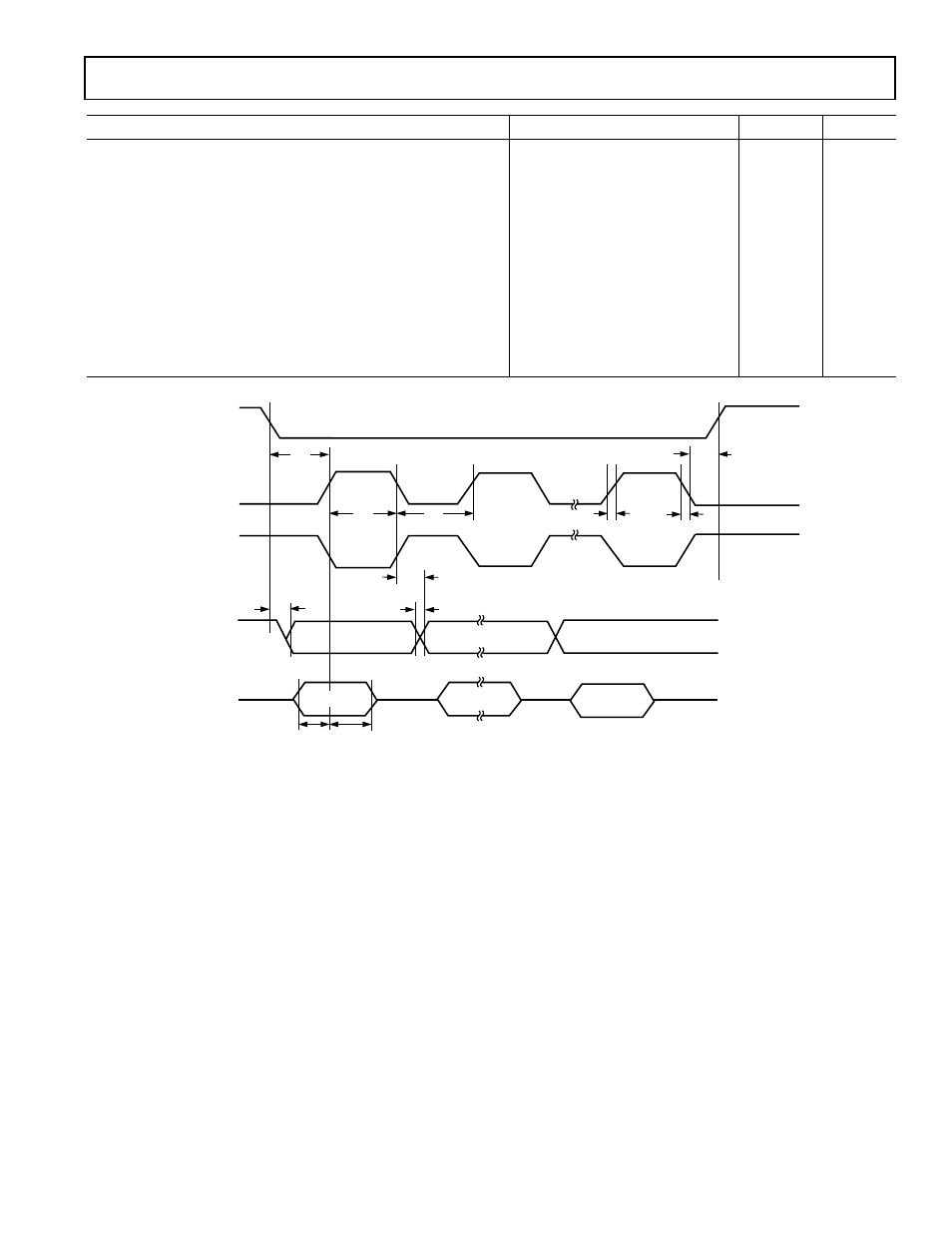

SPI SLAVE MODE TIMING (CPHA = 0)

t

SS

SS to SCLOCK Edge

0

ns

60

t

SL

SCLOCK Low Pulsewidth

330

ns

60

t

SH

SCLOCK High Pulsewidth

330

ns

60

t

DAV

Data Output Valid after SCLOCK Edge

50

ns

60

t

DSU

Data Input Setup Time before SCLOCK Edge

100

ns

60

t

DHD

Data Input Hold Time after SCLOCK Edge

100

ns

60

t

DF

Data Output Fall Time

10

25

ns

60

t

DR

Data Output Rise Time

10

25

ns

60

t

SR

SCLOCK Rise Time

10

25

ns

60

t

SF

SCLOCK Fall Time

10

25

ns

60

t

DOSS

Data Output Valid after

SS Edge

20

ns

60

t

SFS

SS High after SCLOCK Edge

ns

60

t

DAV

t

SFS

MISO

MOSI

SCLOCK

(CPOL=1)

SCLOCK

(CPOL=0)

t

SH

t

SL

t

SR

t

DF

t

DR

t

DSU

t

DHD

t

SS

SS

t

DOSS

MSB

BIT 6 – 1

LSB

BIT 6 – 1

LSB IN

MSB IN

t

SF

Figure 59. SPI Slave Mode Timing (CPHA = 0)