Timer/counter 2 data registers, Th2 and tl2, Rcap2h and rcap2l – Analog Devices ADuC812 User Manual

Page 33: Aduc812

REV. B

ADuC812

–33–

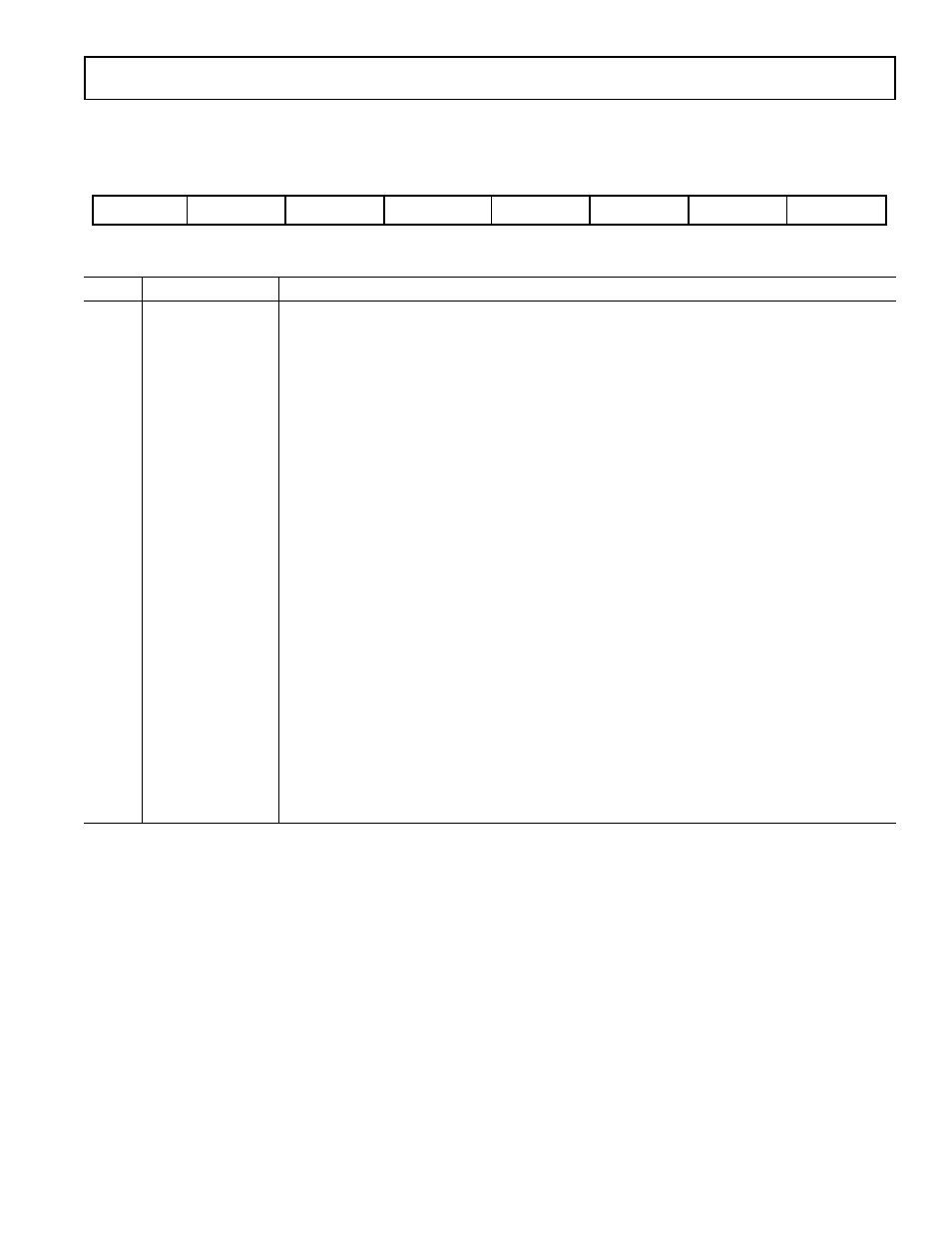

T2CON

Timer/Counter 2 Control Register

SFR Address

C8H

Power-On Default Value

00H

Bit Addressable

Yes

2

F

T

2

F

X

E

K

L

C

R

K

L

C

T

2

N

E

X

E

2

R

T

2

T

N

C

2

P

A

C

Table XVIII. T2CON SFR Bit Designations

Bit

Name

Description

7

TF2

Timer 2 Overflow Flag.

Set by hardware on a timer 2 overflow. TF2 will not be set when either RCLK or TCLK = 1.

Cleared by user software.

6

EXF2

Timer 2 External Flag.

Set by hardware when either a capture or reload is caused by a negative transition on T2EX and

EXEN2 = 1.

Cleared by user software.

5

RCLK

Receive Clock Enable Bit.

Set by user to enable the serial port to use timer 2 overflow pulses for its receive clock in serial port

Modes 1 and 3.

Cleared by user to enable timer 1 overflow to be used for the receive clock.

4

TCLK

Transmit Clock Enable Bit.

Set by user to enable the serial port to use timer 2 overflow pulses for its transmit clock in serial

port Modes 1 and 3.

Cleared by user to enable timer 1 overflow to be used for the transmit clock.

3

EXEN2

Timer 2 External Enable Flag.

Set by user to enable a capture or reload to occur as a result of a negative transition on T2EX if

Timer 2 is not being used to clock the serial port.

Cleared by user for Timer 2 to ignore events at T2EX.

2

TR2

Timer 2 Start/Stop Control Bit.

Set by user to start timer 2.

Cleared by user to stop timer 2.

1

CNT2

Timer 2 Timer or Counter Function Select Bit.

Set by user to select counter function (input from external T2 pin).

Cleared by user to select timer function (input from on-chip core clock).

0

CAP2

Timer 2 Capture/Reload Select Bit.

Set by user to enable captures on negative transitions at T2EX if EXEN2 = 1.

Cleared by user to enable auto-reloads with Timer 2 overflows or negative transitions at T2EX

when EXEN2 = 1. When either RCLK = 1 or TCLK = 1, this bit is ignored and the timer is

forced to autoreload on Timer 2 overflow.

Timer/Counter 2 Data Registers

Timer/Counter 2 also has two pairs of 8-bit data registers

associated with it. These are used as both timer data registers

and timer capture/reload registers.

TH2 and TL2

Timer 2, data high byte and low byte.

SFR Address = CDH, CCH respectively.

RCAP2H and RCAP2L

Timer 2, Capture/Reload byte and low byte.

SFR Address = CBH, CAH respectively.