Aduc812 – Analog Devices ADuC812 User Manual

Page 49

REV. B

ADuC812

–49–

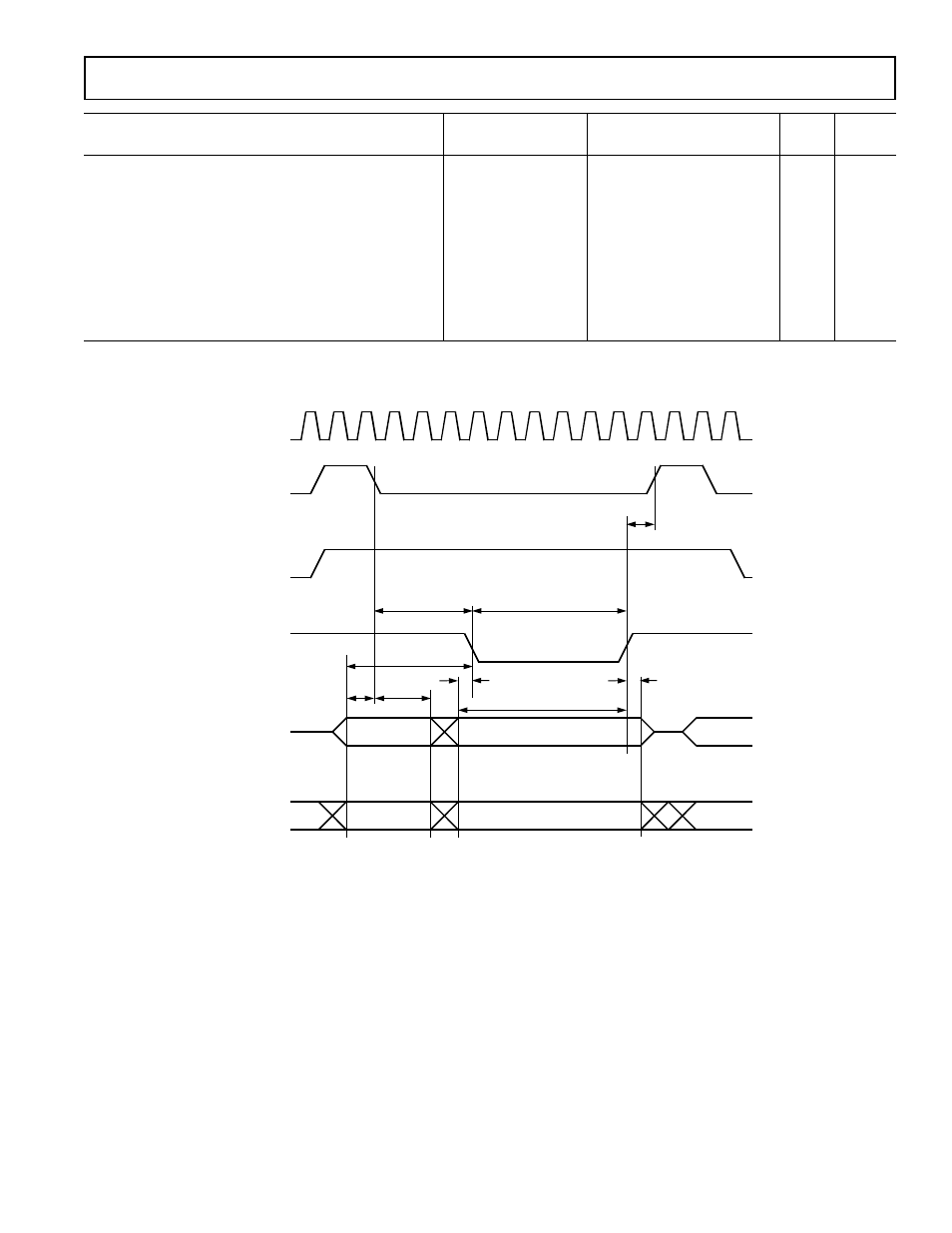

12 MHz

Variable Clock

Parameter

Min

Max

Min

Max

Unit

Figure

EXTERNAL DATA MEMORY WRITE CYCLE

t

WLWH

WR Pulsewidth

400

6t

CK

– 100

ns

54

t

AVLL

Address Valid after ALE Low

43

t

CK

– 40

ns

54

t

LLAX

Address Hold after ALE Low

48

t

CK

– 35

ns

54

t

LLWL

ALE Low to

RD or WR Low

200

300

3t

CK

– 50

3t

CK

+ 50

ns

54

t

AVWL

Address Valid to

RD or WR Low

203

4t

CK

– 130

ns

54

t

QVWX

Data Valid to

WR Transition

33

t

CK

– 50

ns

54

t

QVWH

Data Setup Before

WR

433

7t

CK

– 150

ns

54

t

WHQX

Data and Address Hold after

WR

33

t

CK

– 50

ns

54

t

WHLH

RD or WR High to ALE High

43

123

t

CK

– 40

6t

CK

– 100

ns

54

MCLK

ALE (O)

PSEN (O)

WR (O)

PORT 2 (O)

t

WHLH

t

WLWH

t

LLWL

t

AVWL

t

LLAX

t

AVLL

t

QVWX

t

QVWH

t

WHQX

A0–A7

DATA

A16–A23

A8–A15

Figure 53. External Data Memory Write Cycle