GW Instek PSM-Series Programming Manual User Manual

Page 32

PSM SERIES PROGRAMMABLE POWER SUPPLY

PROGRAMMER MANUAL

⎯ 61 ⎯

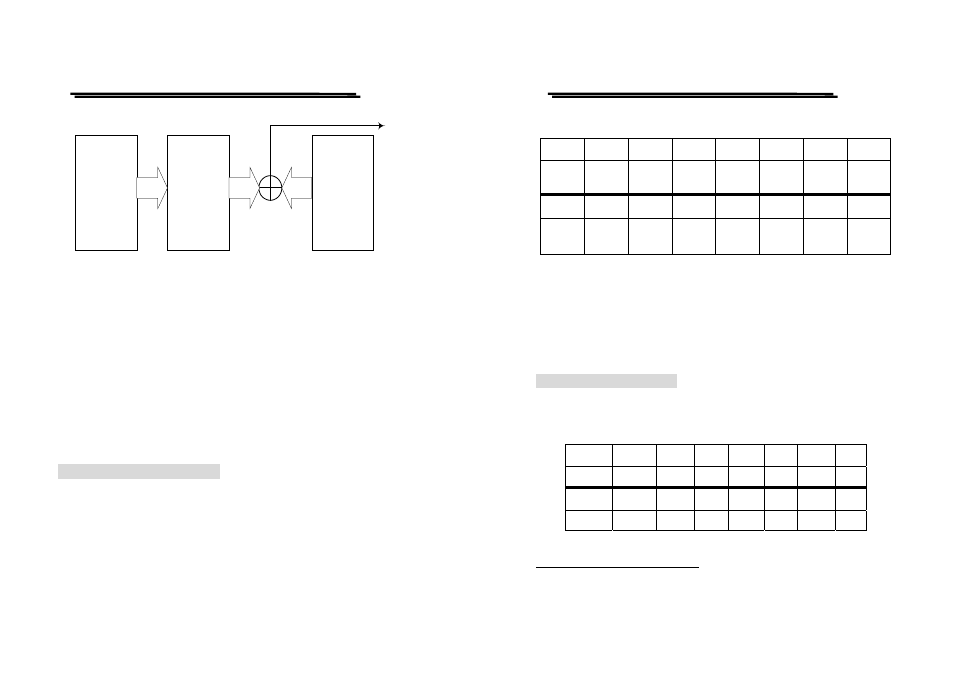

Figure 8: Status registers and related commands

The CONDition register is a read-only register which monitors the present

state of the instrument. The CONDition register updates in real time and the

inputs are not latched or buffered. When a condition monitored by the

CONDition register becomes true, the bit for that condition also becomes

true (1). When the condition is false, the bit is 0.

The read-only EVENt register latches any false-to-true change in condition.

Once the bit in the EVENt register is set, it is no longer affected by changes

in the corresponding bit of the CONDition register. The bit remains set until

the controller reads it. The command *CLS (Clear Status) clears the EVENt

register.

QUEStionable Status Registers.

Table 4 shows the bit designations of the 16 bit QUEStionable Status

Register.

Enable

Register

Event

Register

Condition

Register

To SBR

PSM SERIES PROGRAMMABLE POWER SUPPLY

PROGRAMMER MANUAL

⎯ 62 ⎯

Table 4: QUEStionable Status Register

Bit 15

Bit 14

Bit 13

Bit 12

Bit 11

Bit 10

Bit 9

Bit 8

∗

NU

NU

NU

NU

NU

Summary

OVP

NU

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

NU

NU

NU

NU

NU

NU

Summar

y Current

Summary

Voltage

The command STATus:QUEStionable:CONDtion? Reads the

QUEStionable CONDition register but dose not clear it.

The command STATus:QUEStionable:EVENt? Reads the

QUEStionable EVENt Status register and clears it.

OPERation Status Registers

Table 5 shows the bit designations of the 16 bit OPERation Status Register.

Table 5: OPERation Status Register

Bit 15

Bit 14

Bit 13

Bit 12

Bit 11 Bit 10

Bit 9

Bit 8

NU

NU

NU

NU

NU

NU

NU

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

NU

NU

NU

NU

NU

NU

NU

NU

∗

NU: not used