Timing characteristics – Rainbow Electronics MAX1329 User Manual

Page 10

MAX1329/MAX1330

12-/16-Bit DASs with ADC, DACs, DPIOs, APIOs,

Reference, Voltage Monitors, and Temp Sensor

10

______________________________________________________________________________________

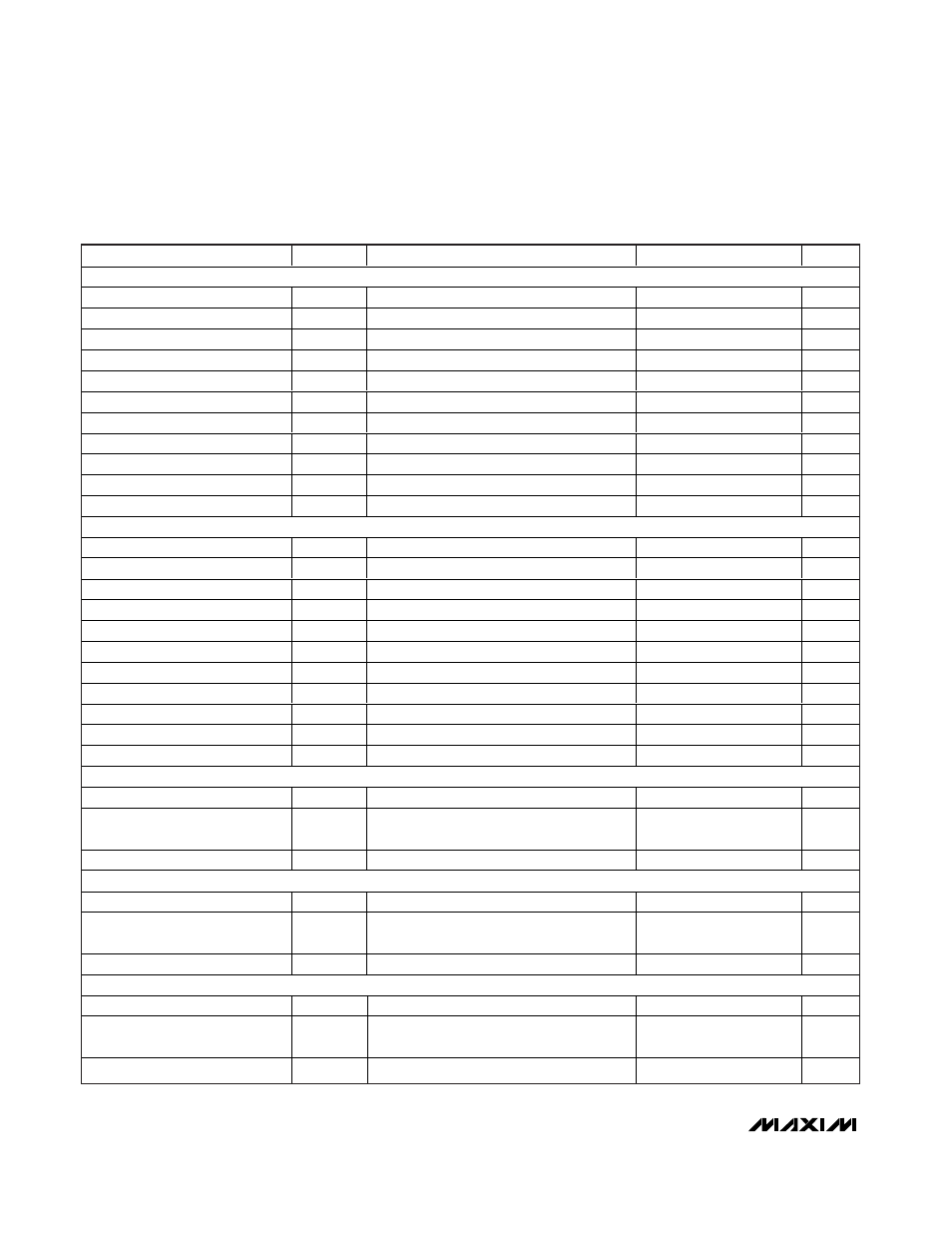

TIMING CHARACTERISTICS

(DV

DD

= 1.8V to 3.6V, AV

DD

= 2.7V to 5.5V, T

A

= T

MIN

to T

MAX

, unless otherwise noted.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

SERIAL-INTERFACE TIMING PARAMETERS (DV

DD

= 2.7V to 3.6V) (Figures 1 and 2)

SCLK Operating Frequency

f

OP

0

20

MHz

SCLK Cycle Time

t

CYC

50

ns

DIN to SCLK Setup

t

DS

15

ns

DIN to SCLK Hold

t

DH

0

ns

SCLK Fall to Output Data Valid

t

DO

20

ns

CS Fall to Output Enable

t

DV

24

ns

CS Rise to Output Disable

t

TR

24

ns

CS to SCLK Rise Setup

t

CSS

15

ns

CS to SCLK Rise Hold

t

CSH

0

ns

SCLK Pulse-Width High

t

CH

20

ns

SCLK Pulse-Width Low

t

CL

20

ns

SERIAL-INTERFACE TIMING PARAMETERS (DV

DD

= 1.8V to 3.6V) (Figures 1 and 2)

SCLK Operating Frequency

f

OP

0

10

MHz

SCLK Cycle Time

t

CYC

100

ns

DIN to SCLK Setup

t

DS

30

ns

DIN to SCLK Hold

t

DH

0

ns

SCLK Fall to Output Data Valid

t

DO

40

ns

CS Fall to Output Enable

t

DV

48

ns

CS Rise to Output Disable

t

TR

48

ns

CS to SCLK Rise Setup

t

CSS

30

ns

CS to SCLK Rise Hold

t

CSH

0

ns

SCLK Pulse-Width High

t

CH

40

ns

SCLK Pulse-Width Low

t

CL

40

ns

DIGITAL PROGRAMMABLE I/O TIMING PARAMETERS (DPIO1–DPIO4, DV

DD

= 2.7V to 3.6V, C

L

=

20pF)

SPI Write to DPIO Output Valid

t

SD

From last SCLK rising edge

50

ns

DPIO Rise/Fall Input to Interrupt

Asserted Delay

t

DI

Interrupt programmed on

RST1 and/or

RST2, corresponding status bits unmasked

55

ns

DPIO Input to Analog Block Delay

t

DA

When controlling ADC, DACs, or switches

40

ns

DIGITAL PROGRAMMABLE I/O TIMING PARAMETERS (DPIO1–DPIO4, DV

DD

= 1.8V to 3.6V, C

L

=

20pF)

SPI Write to DPIO Output Valid

t

SD

From last SCLK rising edge

100

ns

DPIO Rise/Fall Input to Interrupt

Asserted Delay

t

DI

Interrupt programmed on

RST1 and/or

RST2, corresponding status bits unmasked

150

ns

DPIO Input to Analog Block Delay

t

DA

When controlling ADC, DACs, or switches

50

ns

ANALOG PROGRAMMABLE I/O TIMING PARAMETERS (APIO1–APIO4, DV

DD

= 2.7V to 3.6V, AV

DD

= 2.7V to 5.5V, C

L

=

20pF)

SPI Write to APIO Output Valid

t

SD

From last SCLK rising edge

50

ns

APIO Rise/Fall Input to Interrupt

Asserted Delay

t

DI

Interrupt programmed on

RST1 and/or

RST2, corresponding status bits unmasked

50

ns

CS to APIO4 Propagation Delay

t

DCA

AP4MD<1:0> = 11

35

ns