Rainbow Electronics MAX3541 User Manual

Page 15

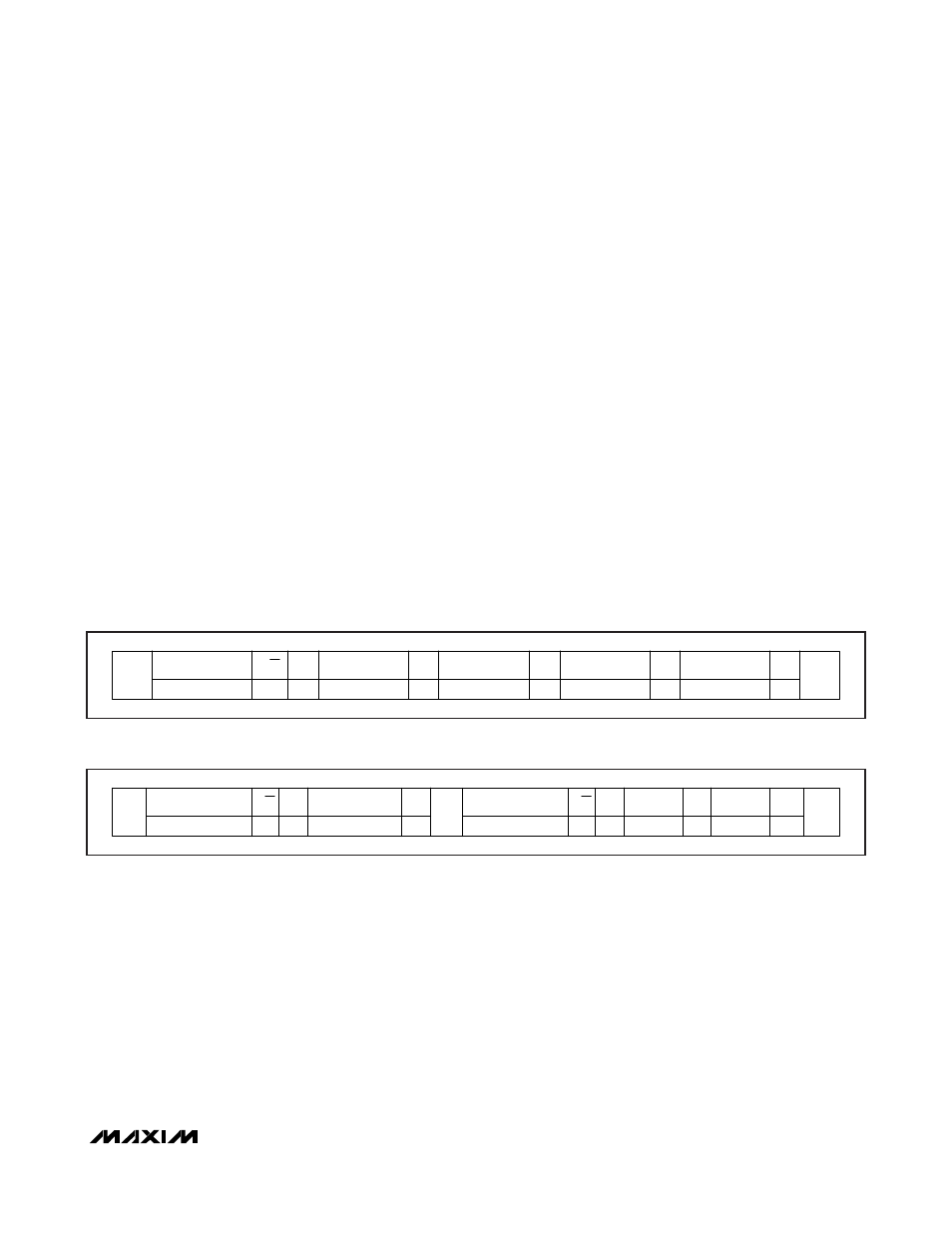

Write Cycle

When addressed with a write command, the MAX3541

allows the master to write to a single register or to multi-

ple successive registers.

A write cycle begins with the bus master issuing a

START condition followed by the seven slave address

bits and a write bit (R/

W = 0). The MAX3541 issues an

ACK if the slave address byte is successfully received.

The bus master must then send to the slave the

address of the first register it wishes to write to. If the

slave acknowledges the address, the master can then

write one byte to the register at the specified address.

Data is written beginning with the most significant bit.

The MAX3541 again issues an ACK if the data is suc-

cessfully written to the register. The master can contin-

ue to write data to the successive internal registers with

the MAX3541 acknowledging each successful transfer,

or it can terminate transmission by issuing a STOP con-

dition. The write cycle does not terminate until the mas-

ter issues a STOP condition.

Figure 2 illustrates an example in which registers 0

through 2 are written with 0x0E, 0xD8, and 0xE1,

respectively.

Read Cycle

A read cycle begins with the bus master issuing a

START condition followed by the seven slave address

bits and a write bit (R/

W = 0). The MAX3541 issues an

A C K i f t h e s l a v e a d d r e s s b y t e i s s u c c e s s f u l l y

received. The master then sends the 8-bit address of

the first register that it wishes to read. The MAX3541

then issues another ACK. Next, the master must issue

a START condition followed by the 7 slave address

bits and a read bit (R/

W = 1). The MAX3541 issues an

ACK if it successfully recognizes its address and

begins sending data from the specified register

address starting with the most significant bit (MSB).

Data is clocked out of the MAX3541 on the rising

edge of SCL. On the 9th rising edge of SCL, the mas-

ter can issue an ACK and continue reading succes-

sive registers or it can issue a NACK followed by a

STOP condition to terminate transmission. The read

cycle does not terminate until the master issues a

STOP condition. Figure 3 illustrates an example in

which registers 0 and 1 are read back.

MAX3541

Complete Single-Conversion

Television Tuner

______________________________________________________________________________________

15

START

WRITE DEVICE

ADDRESS

R/W

11000[ADDR2][ADDR1]

0

—

—

—

—

—

WRITE REGISTER

ADDRESS

0x00

ACK

ACK

ACK

ACK

ACK

WRITE DATA TO

REGISTER 0x00

0x0E

WRITE DATA TO

REGISTER 0x01

0xD8

WRITE DATA TO

REGISTER 0x02

0xE1

STOP

Figure 2. Example: Write Registers 0 Through 2 with 0x0E, 0xD8, and 0xE1, Respectively

START

WRITE DEVICE

ADDRESS

R/W

110000[ADDR2][ADDR1]

WRITE DEVICE

ADDRESS

110000[ADDR2][ADDR1]

0

—

—

WRITE 1ST REGISTER

ADDRESS

0x00

ACK

NACK

—

ACK

READ DATA

REG 0

D7–D0

STOP

R/W

1

—

ACK

READ DATA

REG 1

D7–D0

—

ACK

START

Figure 3. Example: Read Data from Registers 0 and 1