Design procedure, Applications information, Table 1. pulse-width control – Rainbow Electronics MAX3941 User Manual

Page 9

The input data is retimed on the rising edge of CLK+. If

RTEN is connected to ground, the retiming function is dis-

abled and the input data is directly connected to the out-

put stage. Leave CLK+ and CLK- open when retiming is

disabled.

Pulse-Width Control

The pulse-width control circuit can be used to compen-

sate for pulse-width distortion introduced by the EAM.

The differential voltage between PWC+ and PWC-

adjusts the pulse-width compensation. The adjustment

range is typically ±50ps. Optional single-ended opera-

tion is possible by forcing a voltage on the PWC+ pin

while leaving the PWC- pin unconnected. When PWC-

is connected to ground, the pulse-width control circuit

is automatically disabled.

Modulation Output Enable

The MAX3941 incorporates a modulation current-

enable input. When MODEN is low or floating, the mod-

ulation/bias output (OUT) is enabled. When MODEN is

high, the output is switched to the logic 0 state. The

typical enable time is 2ns and the typical disable time

is 2ns.

Design Procedure

Programming the Modulation Voltage

The EAM modulation voltage results from I

MOD

passing

through the EAM impedance (Z

L

) in parallel with the

internal 50

Ω termination resistor (R

OUT

):

To program the desired modulation current, force a

voltage at the MODSET pin (see the Typical Application

Circuit). The resulting I

MOD

current can be calculated

by the following equation:

An internal, independent current source drives a constant

37mA to the modulation circuitry, and any voltage above

V

EE

on the MODSET pin adds to this. The input imped-

ance of the MODSET pin is typically 20k

Ω. Note that the

minimum output voltage is V

EE

+ 1.9V (Figure 5).

Programming the Bias Voltage

As in the case of modulation, the EAM bias voltage

results from I

BIAS

passing through the EAM impedance

(Z

L

) in parallel with the internal 50

Ω termination resistor

(R

OUT

):

To program the desired bias current, force a voltage at

the BIASSET pin (see the Typical Application Circuit).

The resulting I

BIAS

current can be calculated by the fol-

lowing equation:

The input impedance of the BIASSET pin is typically

20k

Ω. Note that the minimum output voltage is V

EE

+

1.9V (Figure 5).

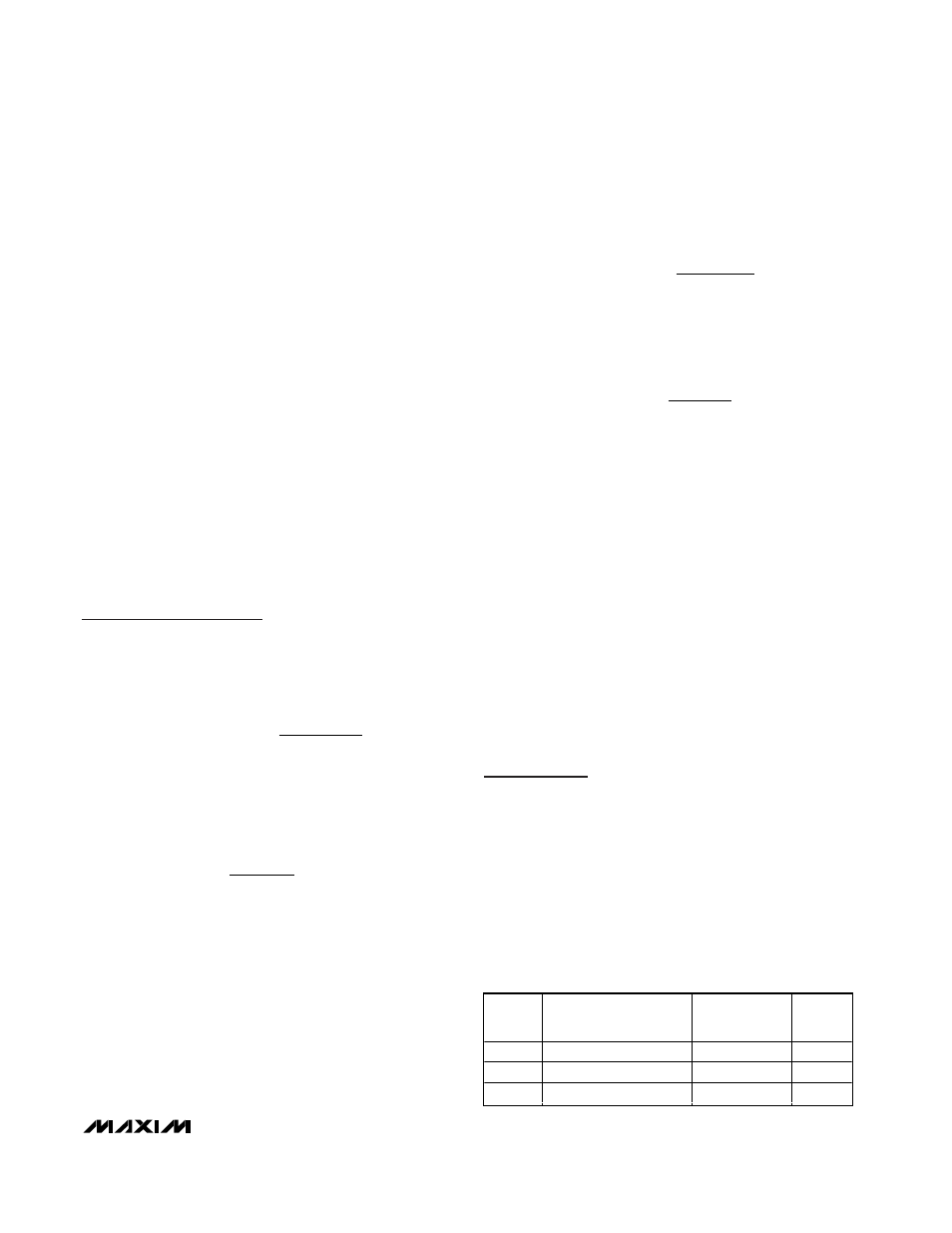

Programming the Pulse-Width Control

Three methods of control are possible when pulse predis-

tortion is desired to minimize distortion at the receiver.

The pulse width can be set with a 2k

Ω potentiometer with

the center tapped to V

EE

(or equivalent fixed resistors),

by applying a voltage to the PWC+ pin, or by applying a

differential voltage across the PWC+ and PWC- pins. See

Table 1 for the desired effect of the pulse-width setting.

Pulse width is defined as (positive pulse width)/((positive

pulse width + negative pulse width)/2).

Input Termination Requirement

The MAX3941 data and clock inputs are CML compati-

ble. However, it is not necessary to drive the IC with a

standard CML signal. As long as the specified input volt-

age swings are met, the MAX3941 operates properly.

Applications Information

Layout Considerations

To minimize loss and crosstalk, keep the connections

between the MAX3941 output and the EAM module as

short as possible. Use good high-frequency layout

techniques and multilayer boards with an uninterrupted

ground plane to minimize EMI and crosstalk. Circuit

boards should be made using low-loss dielectrics. Use

controlled-impedance lines for the clock and data

inputs as well as for the data output. Be sure to filter the

power supply with capacitors placed close to the IC.

I

V

3

BIAS

BIASSET

≈

6 4

.

Ω

V

I

Z

R

Z

R

BIAS

BIAS

L

OUT

L

OUT

≈

Ч

Ч

+

I

V

11.1

MOD

MODSET

≈

+

Ω

37mA

V

I

Z

R

Z

R

MOD

MOD

L

OUT

L

OUT

≈

Ч

Ч

+

MAX3941

10Gbps EAM Driver with Integrated

Bias Network

_______________________________________________________________________________________

9

Table 1. Pulse-Width Control

PULSE-

WIDTH

(%)

R

PWC+

, R

PWC-

FOR

R

PWC+

+ R

PWC-

= 2k

Ω

V

PWC+

(PWC-

OPEN)

(V)

V

PWC+

-

V

PWC-

(V)

100

R

PWC+

= R

PWC-

V

EE

+ 1

0

>100

R

PWC+

> R

PWC-

> V

EE

+ 1

>0

<100

R

PWC+

< R

PWC-

< V

EE

+ 1

<0