At83c24 – Rainbow Electronics AT83C24NDS User Manual

Page 32

32

4234F–SCR–10/05

AT83C24

Rise and Fall Slew rate

0.2

0.12

V/ns

CLASS A

CCLK from 0.5 to 4.2V

CLASS B

CCLK from 0.5 to 0.85 x

CVCC

Low level voltage stability

(taking into account PCB design)

-0.25

0.5

V

CLASS A&B&C

High level voltage stability

(taking into account PCB design)

4.2

2.35

CVCC-0.4

CVCC+0.25

CVCC+0.25

CVCC+0.25

V

CVCC = CLASS A

CVCC = CLASS B

CLASS C

CCLK

Smart card clock frequency

24

MHz

C

L

= 30pF, CLK=48MHz

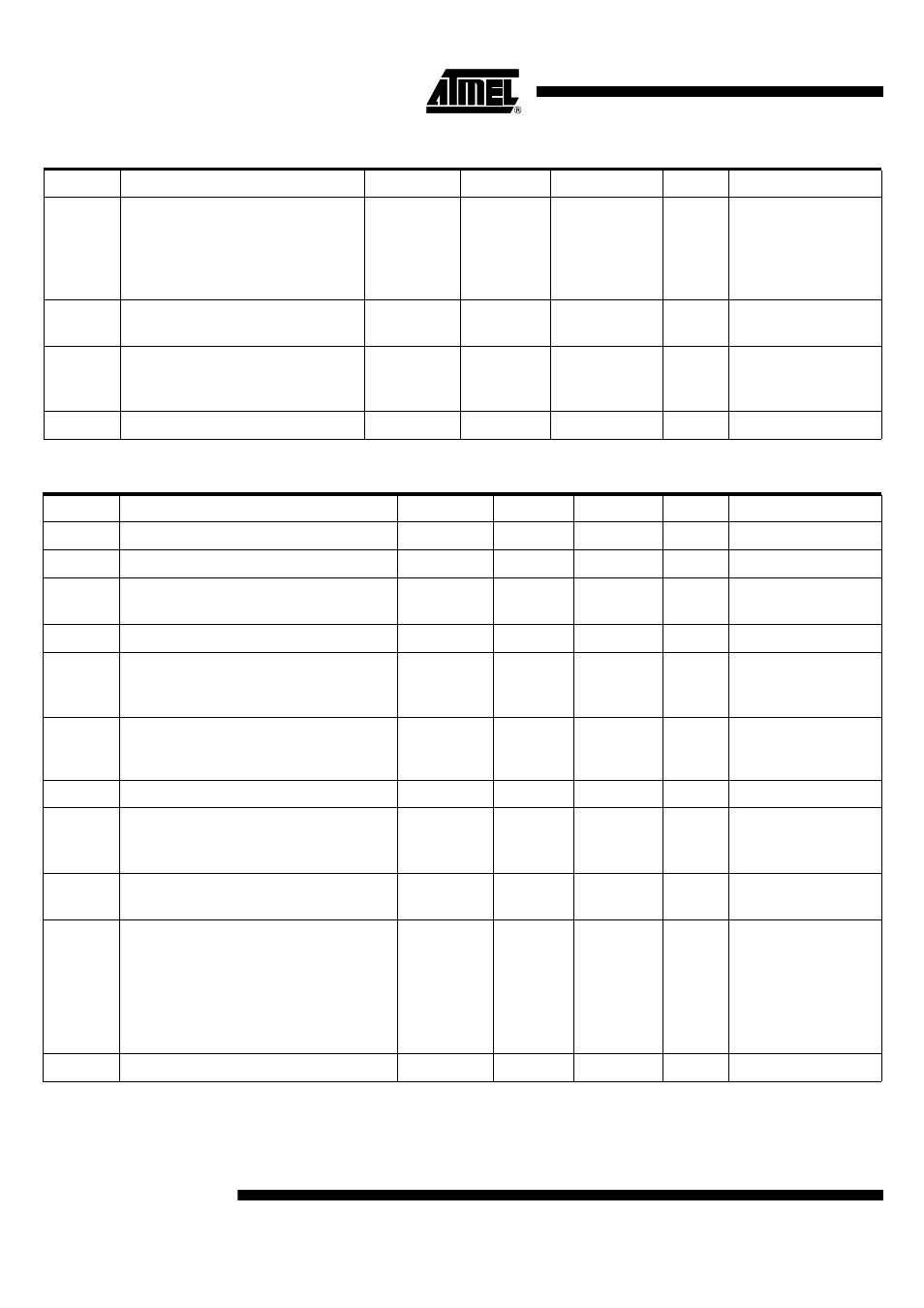

Table 23. Smart Card Clock (CCLK pin) (Continued)

Symbol

Parameter

Min

Typ

Max

Unit

Test Conditions

Table 24. Smart Card I/O (CIO, CC4, CC8 pins)

Symbol

Parameter

Min

Typ

Max

Unit

Test Conditions

V

IL

Input Low-voltage

-0.3V

0.8

V

I

IL

= 500 µA

I

IL

Input Low Current

700

µA

CVCC = CLASS A&B&C

V

IH

Input High Voltage

0.6 x CVCC

0.7 x CVCC

CVCC

CVCC

V

CVCC = CLASS A

CVCC = CLASS B & C

I

IH

Input High Current

-20

+20

μA

V

OL

Output Low-voltage

0

0.45

0.3

0.3

V

I

OL

= -1 mA CLASS A

I

OL

= -1 mA CLASS B

I

OL

= -1 mA CLASS C

V

OH

Output High Voltage

0.75 x CVCC

0.9 x CVCC

CVCC

CVCC

V

I

OH

= 40

μA CLASS

A&B&C

I

OH

= 0

μ

A, CLASS A&B

I

OS

Output Short Circuit Current

-15

+15

mA

Short to GND or CVCC

Low level voltage stability

(taking into account PCB design)

-0.25

-0.25

-0.25

0.6

0.4

0.4

V

CLASS A

CLASS B

CLASS C

High level voltage stability

(taking into account PCB design)

CVCC-0.5

CVCC+0.25

V

CVCC = CLASS A&B&C

t

R

t

F

Output rise and fall time

0.1

μ

s

C

L

= 65 pF

CLASS A:

measurement between

0.6V and 70% of CVCC

CLASS B & C:

measurement between

0.4V and 70% of CVCC

t

R

t

F

Input rise and fall time

1

μ

s

C

L

= 65 pF