At83c24 – Rainbow Electronics AT83C24NDS User Manual

Page 22

22

4234F–SCR–10/05

AT83C24

Notes:

1. When this register is changed, a special logic insures no glitch occurs on the CCLK pin and

actual configuration changes can be delayed by half a period to two periods of CCLK.

2. CCLK must be stopped with CKSTOP bit before switching from CKS = (0, 1, 2, 3, 6, 7) to CKS

= (4, 5) or vice versa.

3. When DCK = 0, only CKS=4 and CKS=5 are allowed.

4. The user can’t directly select A2 or A2/2 after a reset or when switching from CKS = (0, 1, 2, 3,

6, 7) to CKS = (4, 5). To select A2, the user should select A2/2 first and after A2. To select

A2/2, the user should select A2 first and after A2/2.

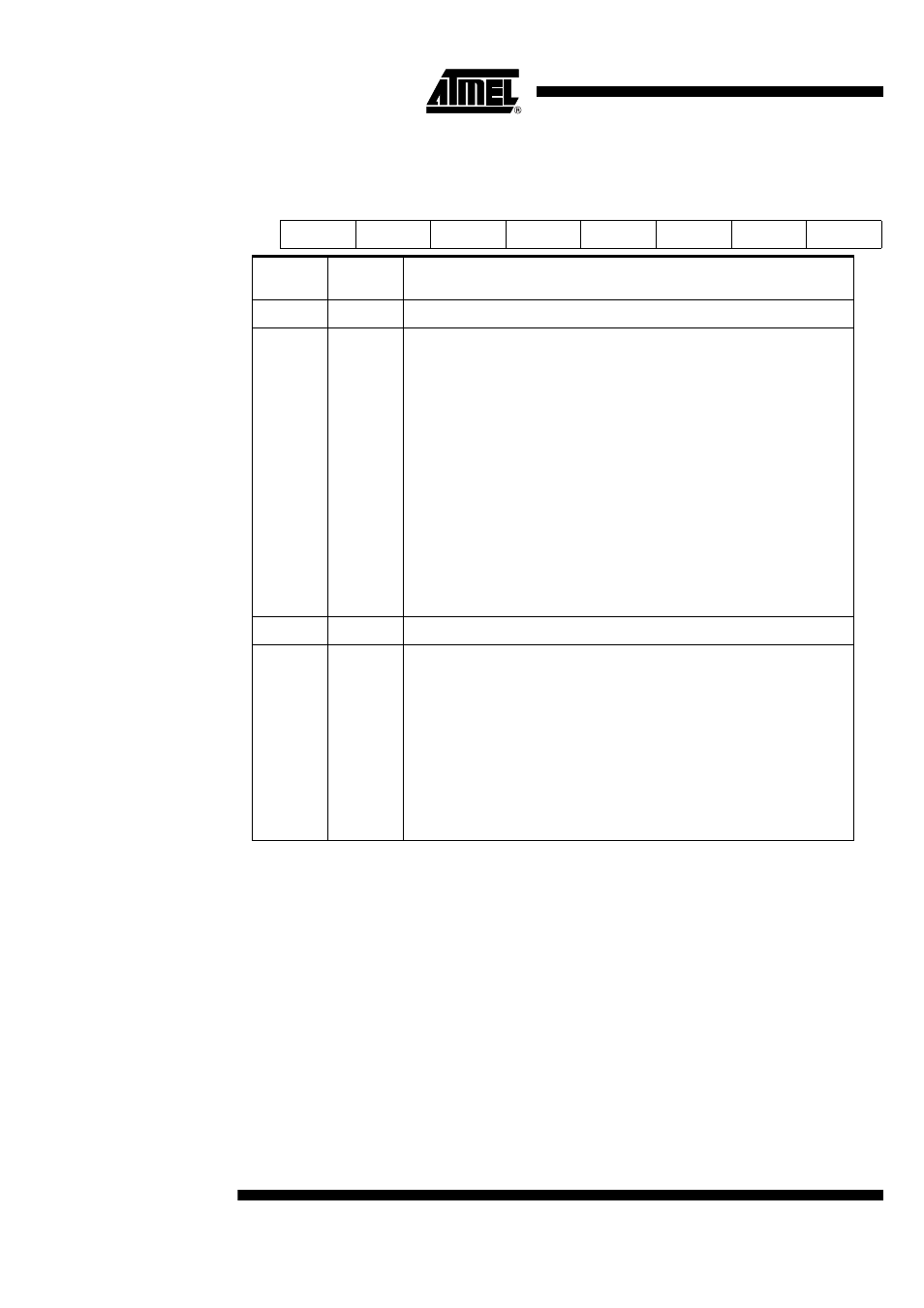

Table 8. CONFIG2 (Config Byte 2)

7

6

5

4

3

2

1

0

X

DCK2

DCK1

DCK0

X

CKS2

CKS1

CKS0

Bit

Number

Bit

Mnemonic

Description

7

X

This bit should not be set.

6-4

DCK[2:0]

DC/DC Clock prescaler factor

DCCLK is the DC/DC clock. It is the division of CLK input by DCK prescaler.

DCK = 0: prescaler factor equals 1 (CLK = 4 to 4.61MHz)

DCK [2:0] = 1: prescaler factor equals 2 (CLK = 7 to 9.25MHz)

DCK [2:0] = 2: prescaler factor equals 4 (CLK = 14 to 18.5 MHz)

DCK [2:0] = 3: prescaler factor equals 6 (CLK = 21 to 27.6 MHz)

DCK [2:0] = 4: prescaler factor equals 8 (CLK = 28 to 34.8 MHz)

DCK [2:0] = 5: prescaler factor equals 10 (CLK = 35 to 43 MHz)

DCK [2:0] = 6: prescaler factor equals 12 (CLK = 43.1 to 48 MHz)

DCK [2:0] = 7: reserved

The reset value is 1.

DCCLK must be as close as possible to 4 MHz with a duty cycle of 50%.

DCK must be programmed before starting the DC/DC.

The other values of CLK are not allowed.

DCK has to be properly configured before resetting the STEPREG bit.

3

X

This bit should not be set.

2-0

CKS[2:0]

Card Clock prescaler factor

CKS [2:0] = 0: CCLK = CLK (then the maximum frequency on CLK is 24 MHz)

CKS [2:0] = 1: CCLK = DCCLK (DC/DC clock)

CKS [2:0] = 2: CCLK = DCCLK / 2

CKS [2:0] = 3: CCLK = DCCLK / 4

CKS [2:0] = 4: CCLK = A2

CKS [2:0] = 5: CCLK = A2 / 2

CKS [2:0] = 6: CCLK = CLK / 2

CKS [2:0] = 7: CCLK = CLK / 4

The reset value is 0.