Watchdog programming – Rainbow Electronics T89C5115 User Manual

Page 63

63

T89C5115

4128A–8051–04/02

WatchDog Programming

The three lower bits (S0, S1, S2) located into WDTPRG register permit to program the

WDT duration.

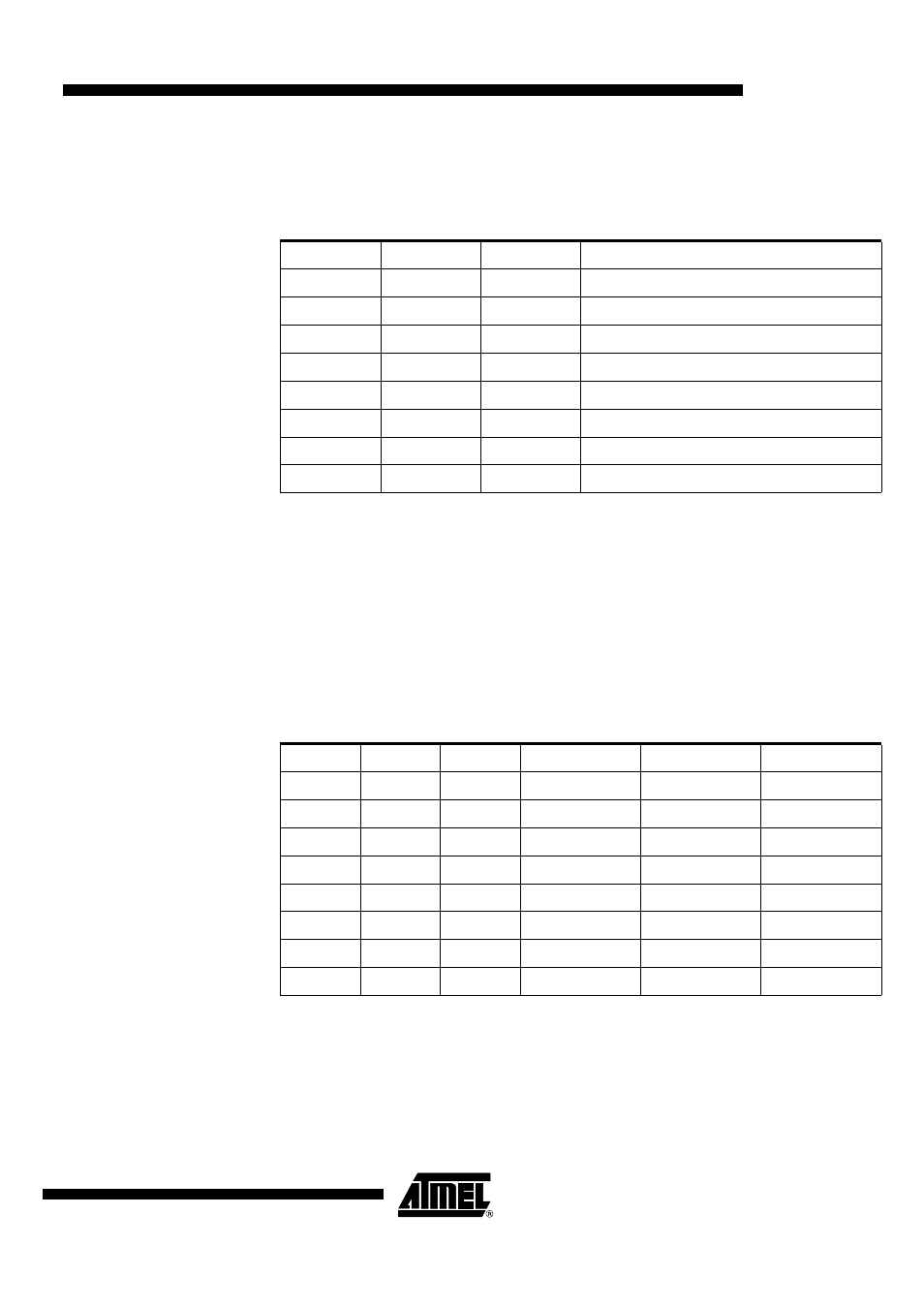

Table 43. Machine Cycle Count

To compute WD Time-Out, the following formula is applied:

Note:

Svalue represents the decimal value of (S2 S1 S0)

The following table indicates the computed Time-Out value for Fosc

XTAL

= 12 MHz in X1

mode

Table 44. Time-Out Computation

S2

S1

S0

Machine Cycle Count

0

0

0

2

14

- 1

0

0

1

2

15

- 1

0

1

0

2

16

- 1

0

1

1

2

17

- 1

1

0

0

2

18

- 1

1

0

1

2

19

- 1

1

1

0

2

20

- 1

1

1

1

2

21

- 1

S2

S1

S0

Fosc = 12 MHz

Fosc = 16 MHz

Fosc = 20 MHz

0

0

0

16.38 ms

12.28 ms

9.82 ms

0

0

1

32.77 ms

24.57 ms

19.66 ms

0

1

0

65.54 ms

49.14 ms

39.32 ms

0

1

1

131.07 ms

98.28 ms

78.64 ms

1

0

0

262.14 ms

196.56 ms

157.28 ms

1

0

1

524.29 ms

393.12 ms

314.56 ms

1

1

0

1.05 sec

786.24 ms

629.12 ms

1

1

1

2.10 sec

1.57 s

1.25 ms

FTime

Out

F

w d

12

2

14

2

Svalue

Ч

(

)

1

–

(

)

Ч

-------------------------------------------------------------------

=

–

- MAX5151 (16 pages)

- MAXQ3108 (64 pages)

- MAX5661 (39 pages)

- MAX6691 (7 pages)

- MAX5362 (12 pages)

- ADC10158 (26 pages)

- MAX8922L (14 pages)

- MAX8596Z (8 pages)

- MAX7491 (18 pages)

- MAX15040 (15 pages)

- MAX5177 (16 pages)

- ADC08138 (22 pages)

- MAX5961 (42 pages)

- T89C51RD2 (86 pages)

- MAX16055 (9 pages)

- MAX6659 (17 pages)

- ADC0820 (20 pages)

- MAX6678 (19 pages)

- MAX8884Z (15 pages)

- MAX16915 (9 pages)

- MAX8620 (18 pages)

- MAX5144 (12 pages)

- MAX6670 (8 pages)

- MAX8760 (39 pages)

- W78C32C (14 pages)

- MX7533 (8 pages)

- MAX8727 (13 pages)

- MAX9053 (15 pages)

- W78C54 (16 pages)

- MAX8614B (15 pages)

- W90N740 (219 pages)

- MAX6626 (13 pages)

- ADC10738 (30 pages)

- MAX17000 (31 pages)

- MAX5051 (21 pages)

- MAXQ1004 (18 pages)

- MAX6871 (51 pages)

- MX7847 (12 pages)

- MAX6608 (6 pages)

- MAX17083 (15 pages)

- MAX6641 (17 pages)

- MAX5251 (16 pages)

- MAX6338 (8 pages)

- MAX6690 (16 pages)

- MAX8668 (18 pages)