Registers – Rainbow Electronics T89C5115 User Manual

Page 45

45

T89C5115

4128A–8051–04/02

For slaves A and B, bit 2 is a don’t care bit; for slave C, bit 2 is set. To communicate with

all of the slaves, the master must send an address FFh. To communicate with slaves A

and B, but not slave C, the master can send and address FBh.

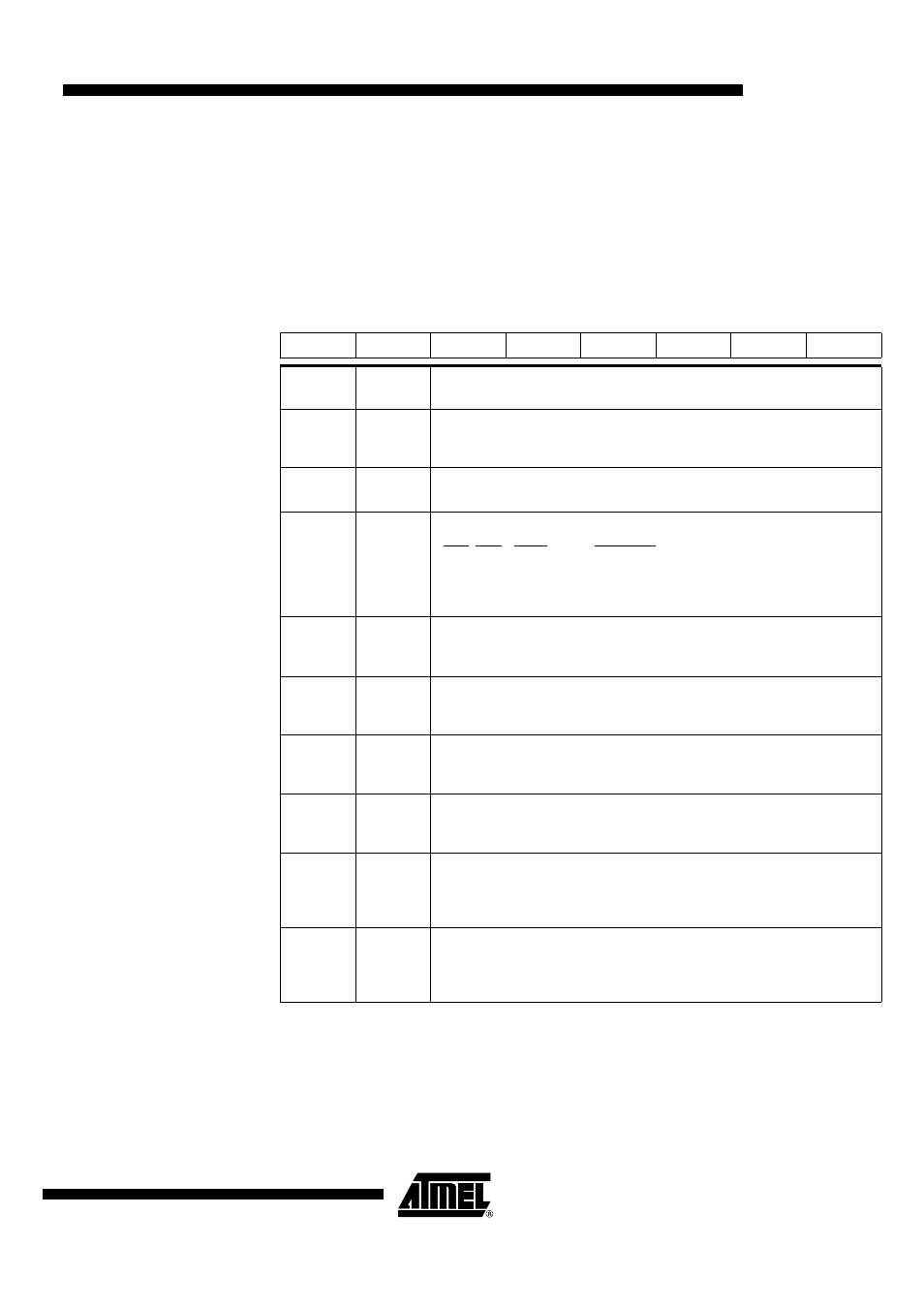

Registers

Table 26. SCON Register

SCON (S:98h)

Serial Control Register

Reset Value = 0000 0000b

Bit addressable

7

6

5

4

3

2

1

0

FE/SM0

SM1

SM2

REN

TB8

RB8

TI

RI

Bit

Number

Bit

Mnemonic

Description

7

FE

Framing Error bit (SMOD0 = 1)

Clear to reset the error state, not cleared by a valid stop bit.

Set by hardware when an invalid stop bit is detected.

–

SM0

Serial port Mode bit 0 (SMOD0 = 0)

Refer to SM1 for serial port mode selection.

6

SM1

Serial port Mode bit 1

SM0 SM1

Mode

Baud Rate

0

0

Shift Register F

XTAL

/12 (or F

XTAL

/6 in mode X2)

0

1

8-bit UART

Variable

1

0

9-bit UART

F

XTAL

/64 or F

XTAL

/32

1

1

9-bit UART

Variable

5

SM2

Serial port Mode 2 bit/Multiprocessor Communication Enable bit

Clear to disable multiprocessor communication feature.

Set to enable multiprocessor communication feature in mode 2 and 3.

4

REN

Reception Enable bit

Clear to disable serial reception.

Set to enable serial reception.

3

TB8

Transmitter Bit 8/Ninth bit to transmit in modes 2 and 3

Clear to transmit a logic 0 in the 9th bit.

Set to transmit a logic 1 in the 9th bit.

2

RB8

Receiver Bit 8/Ninth bit received in modes 2 and 3

Cleared by hardware if 9th bit received is a logic 0.

Set by hardware if 9th bit received is a logic 1.

1

TI

Transmit Interrupt flag

Clear to acknowledge interrupt.

Set by hardware at the end of the 8th bit time in mode 0 or at the beginning of the

stop bit in the other modes.

0

RI

Receive Interrupt flag

Clear to acknowledge interrupt.

Set by hardware at the end of the 8th bit time in mode 0, see Figure 20 and

Figure 21 in the other modes.