Electrical characteristics (continued) – Rainbow Electronics MAX17480 User Manual

Page 6

MAX17480

AMD 2-/3-Output Mobile Serial

VID Controller

6

_______________________________________________________________________________________

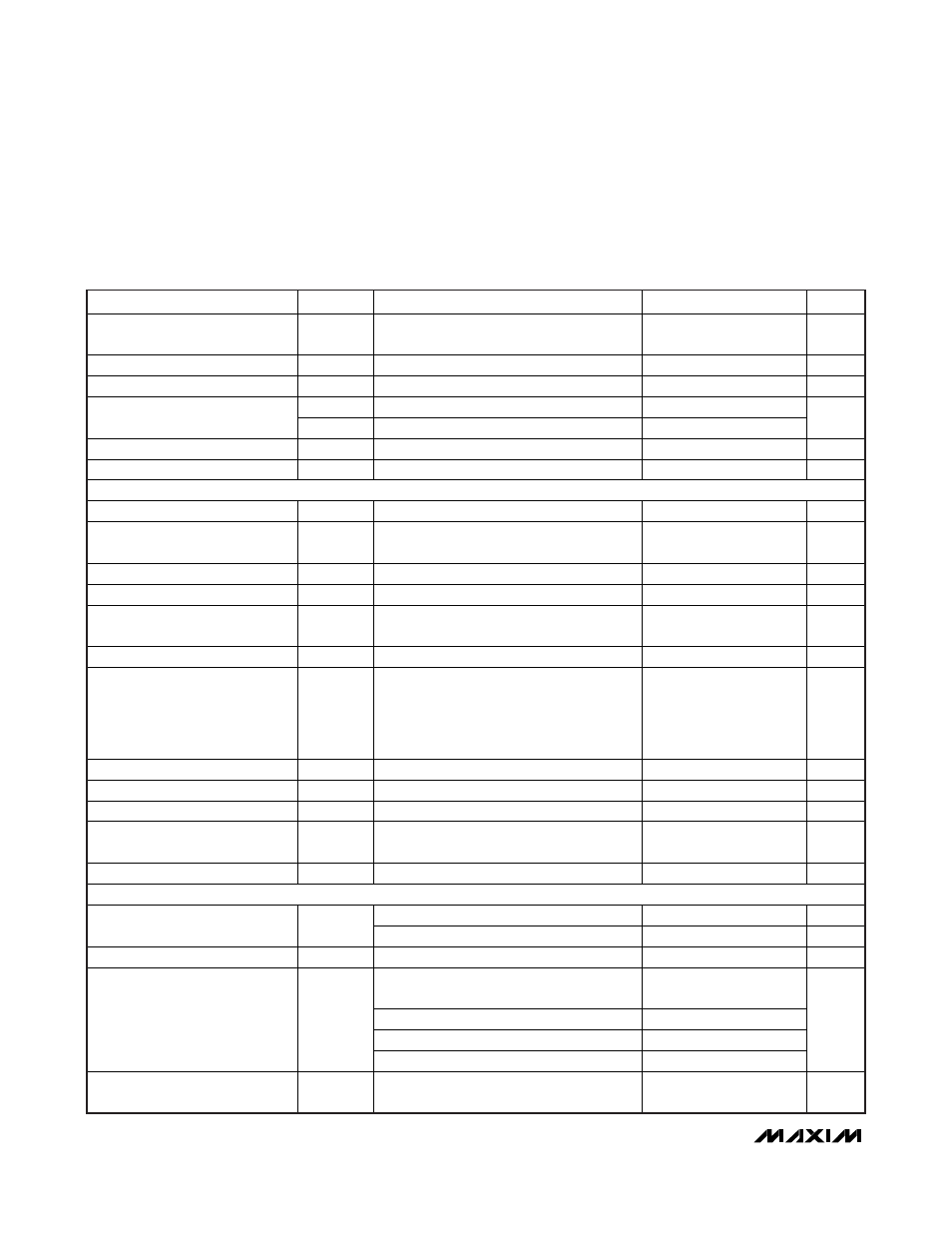

ELECTRICAL CHARACTERISTICS (continued)

(Circuit of Figure 2, V

IN

= 12V, V

CC

= V

DD

= V

IN3

= SHDN = PGD_IN = 5V, V

DDIO

= 1.8V, OPTION = GNDS_ = AGND = PGND,

FBDC_ = FBAC_ = OUT3 = CSP_ = CSN_ = 1.2V, all DAC codes set to the 1.2V code, T

A

= 0°C to +85°C, unless otherwise noted.

Typical values are at T

A

= +25

°C.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

DH_ Gate-Driver Source/Sink

Current

I

DH

_

DH_ forced to 2.5V, BST_ - LX_ forced to 5V

2.2

A

DL_ Gate-Driver Source Current

I

DL

_

DL_ forced to 2.5V

2.7

A

DL_ Gate-Driver Sink Current

I

DL

_

(SINK)

DL_ forced to 2.5V

8

A

t

DH

_

DL

DH_ low to DL_ high

9

20

35

Dead Time

t

DL

_

DH

DL_ low to DH_ high

9

20

35

ns

Internal BST1, BST2 Switch R

ON

BST1, BST2 to V

DD

, I

BST1

= I

BST2

= 10mA

10

20

Internal BST3 Switch R

ON

BST3 to V

DD

, I

BST3

= 10mA

10

20

2-WIRE I

2

C BUS LOGIC INTERFACE

SVI Logic-Input Current

SVC, SVD, T

A

= +25°C

-1

+1

µA

SVI Logic-Input Threshold

SVC, SVD, rising edge, hysteresis 0.14 x

V

DDIO

(V)

0.3 x

V

DDIO

0.7 x

V

DDIO

V

SVC Clock Frequency

f

SVC

3.4

MHz

START Condition Hold Time

t

HD;STA

160

ns

Repeated START Condition

Setup Time

t

SU;STA

160

ns

STOP Condition Setup Time

t

SU;STO

160

ns

Data Hold

t

HD;DAT

A master device must internally provide a

hold time of at least 300ns for the SVD

signal (referred to the V

IHMIN

of SVC signal)

to bridge the undefined region of SVC’s

falling edge

70

ns

Data Setup Time

t

SU;DAT

10

ns

SVC Low Period

t

LOW

160

ns

SVC High Period

t

HIGH

Measured from 10% to 90% of V

DDIO

60

ns

SVC/SVD Rise and Fall Time

t

R

, t

F

Input filters on SVD and SVC suppress

noise spike less than 50ns

40

ns

Pulse Width of Spike Suppression

20

ns

INPUTS AND OUTPUTS

SHDN, PGD_IN, T

A

= +25°C

-1

+1

µA

Logic-Input Current

ILIM3, OPTION, T

A

= +25°C

-200

+200

nA

Logic-Input Levels

SHDN, rising edge, hysteresis = 225mV

0.8

2.0

V

High, OPTION, ILIM3

V

CC

-

0.4

3.3V,

OPTION

2.75 3.85

2V,

OPTION

1.65 2.35

Input Logic Levels

Low, OPTION, ILIM3

0.4

V

PGD_IN Logic-Input Threshold

PGD_IN, rising edge, hysteresis = 65mV

0.3 x

V

DDIO

0.7 x

V

DDIO

V