Rainbow Electronics MAX17480 User Manual

Page 44

MAX17480

AMD 2-/3-Output Mobile Serial

VID Controller

44

______________________________________________________________________________________

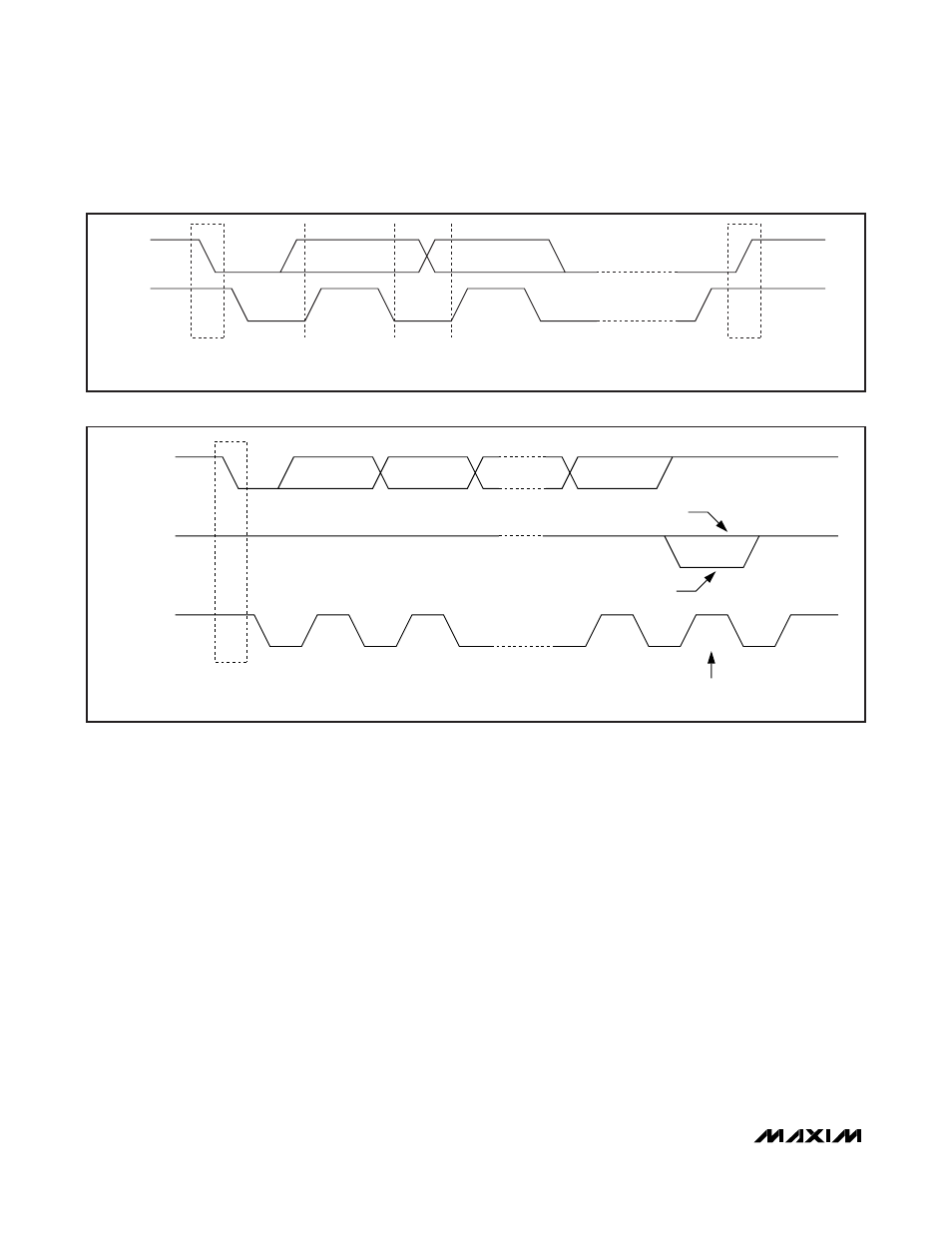

Bus Not Busy

The SVI bus is not busy when both data and clock lines

remain high. Data transfers can be initiated only when

the bus is not busy. Figure 13 shows the SVI bus

acknowledge.

Start Data Transfer (S)

Starting from an idle bus state (both SVC and SVD are

high), a high-to-low transition of the data (SVD) line while

the clock (SVC) is high determines a START condition.

All commands must be preceded by a START condition.

Stop Data Transfer (P)

A low-to-high transition of the SDA line while the clock

(SVC) is high determines a STOP condition. All opera-

tions must be ended with a STOP condition.

Slave Address

After generating a START condition, the bus master

transmits the slave address consisting of a 7-bit device

code (110xxxx) for the MAX17480. Since the

MAX17480 is a write-only device, the eighth bit of the

slave address is 0. The MAX17480 monitors the bus for

its corresponding slave address continuously. It gener-

ates an acknowledge bit if the slave address was true

and it is not in a programming mode.

SVD Data Valid

The state of the data line represents valid data when,

after a START condition, the data line is stable for the

duration of the high period of the clock signal. The data

on the line must be changed during the low period of

the clock signal. There is one clock pulse per bit of data.

Acknowledge

Each receiving device, when addressed, is obliged to

generate an acknowledge after the reception of each

byte. The master device must generate an extra clock

pulse that is associated with this acknowledge bit. The

device that acknowledges has to pull down the SVD

line during the acknowledge clock pulse so that the

SVD line is stable low during the high period of the

acknowledge-related clock pulse. Of course, setup and

hold times must be taken into account. See Figure 13.

DATA OUTPUT

BY MASTER

DATA OUTPUT

BY MAX17480

SVC FROM

MASTER

S

START

CONDITION

D7

1

CLK1

2

CLK2

8

CLK8

9

CLK9

D6

D0

NOT ACKNOWLEDGE

ACKNOWLEDGE

ACKNOWLEDGE

CLOCK PULSE

Figure 13. SVI Bus Acknowledge

SVD

SVC

S

START

CONDITION

STOP

CONDITION

DATA LINE

STABLE

DATA VALID

CHANGE

OF DATA

ALLOWED

P

Figure 12. SVI Bus START, STOP, and Data Change Conditions