Pin description (continued) – Rainbow Electronics MAX17480 User Manual

Page 18

MAX17480

AMD 2-/3-Output Mobile Serial

VID Controller

18

______________________________________________________________________________________

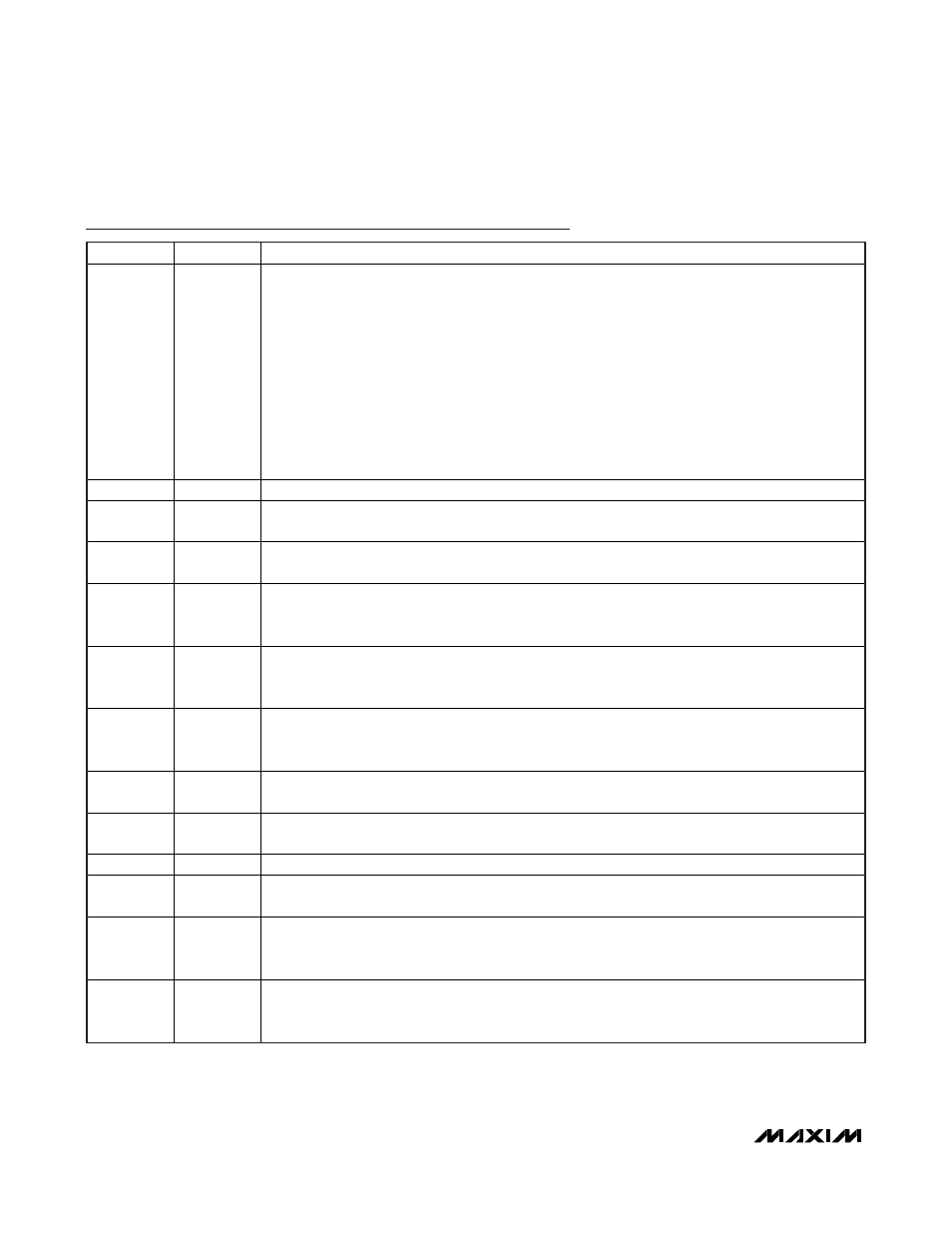

Pin Description (continued)

PIN

NAME

FUNCTION

20 PWRGD

Open-Drain Power-Good Output. PWRGD is the wired-OR open-drain output of all three SMPS

outputs.

PWRGD is forced high impedance whenever the slew-rate controller is active (output voltage

transitions).

During startup, PWRGD is held low for an additional 20µs after the MAX17480 reaches the startup

boot voltage set by the SVC and SVD pins. The MAX17480 stores the boot VID when PWRGD first

goes high. The stored boot VID is cleared by rising

SHDN.

PWRGD is forced low in shutdown.

When SMPS is in pulse-skipping mode, the upper PWRGD threshold comparator for the respective

SMPS is blanked during a downward VID transition. The upper PWRGD threshold comparator is re-

enabled once the output is in regulation (Figure 6).

21

DH2

SMPS2 High-Side Gate-Driver Output. DH2 swings from LX2 to BST2. Low in shutdown.

22 LX2

SMPS2 Inductor Connection. LX2 is the internal lower supply rail for the DH2 high-side gate driver.

Also used as an input to SMPS2’s zero-crossing comparator.

23 BST2

Boost Flying Capacitor Connection for the DH2 High-Side Gate Driver. An internal switch between

V

DD

and BST2 charges the flying capacitor during the time the low-side FET is on.

24 DL2

SMPS2 Low-Side Gate-Driver Output. DL2 swings from GND2 to V

DD

. DL2 is forced low in shutdown.

DL2 is also forced high when an output overvoltage fault is detected. DL2 is forced low in skip

mode after an inductor current zero crossing (GND2 - LX2) is detected.

25 V

DD

Supply Voltage Input for the DL_ Drivers. V

DD

is also the supply voltage used to internally recharge

the BST_ flying capacitors during the off-time. Connect V

DD

to the 4.5V to 5.5V system supply

voltage. Bypass V

DD

to GND with a 2.2µF or greater ceramic capacitor.

26 DL1

SMPS1 Low-Side Gate-Driver Output. DL1 swings from GND1 to V

DD

. DL1 is forced low in shutdown.

DL1 is also forced high when an output overvoltage fault is detected. DL1 is forced low in skip

mode after an inductor current zero crossing (GND1 - LX1) is detected.

27 BST1

Boost Flying Capacitor Connection for the DH1 High-Side Gate Driver. An internal switch between

V

DD

and BST1 charges the flying capacitor during the time the low-side FET is on.

28 LX1

SMPS1 Inductor Connection. LX1 is the internal lower supply rail for the DH1 high-side gate driver.

Also used as an input to SMPS1’s zero-crossing comparator.

29

DH1

SMPS1 High-Side Gate-Driver Output. DH1 swings from LX1 to BST1. Low in shutdown.

30

VRHOT

Active-Low Open-Drain Output of Internal Comparator.

VRHOT is pulled low when the voltage at

THRM goes below 1.5V (30% of V

CC

).

VRHOT is high impedance in shutdown.

31 THRM

Input of Internal Comparator. Connect the output of a resistor- and thermistor-divider (between V

CC

and GND) to THRM. Select the components so the voltage at THRM falls below 1.5V (30% of V

CC

)

at the desired high temperature.

32 V

CC

Controller Supply Voltage. Connect to a 4.5V to 5.5V source. Bypass to GND with a 1µF minimum

capacitor. A V

CC

UVLO event that occurs while the IC is functioning is latched, and can only be

cleared by cycling V

CC

power or by toggling

SHDN.