Pin description (continued) – Rainbow Electronics MAX17480 User Manual

Page 17

MAX17480

AMD 2-/3-Output Mobile Serial

VID Controller

______________________________________________________________________________________

17

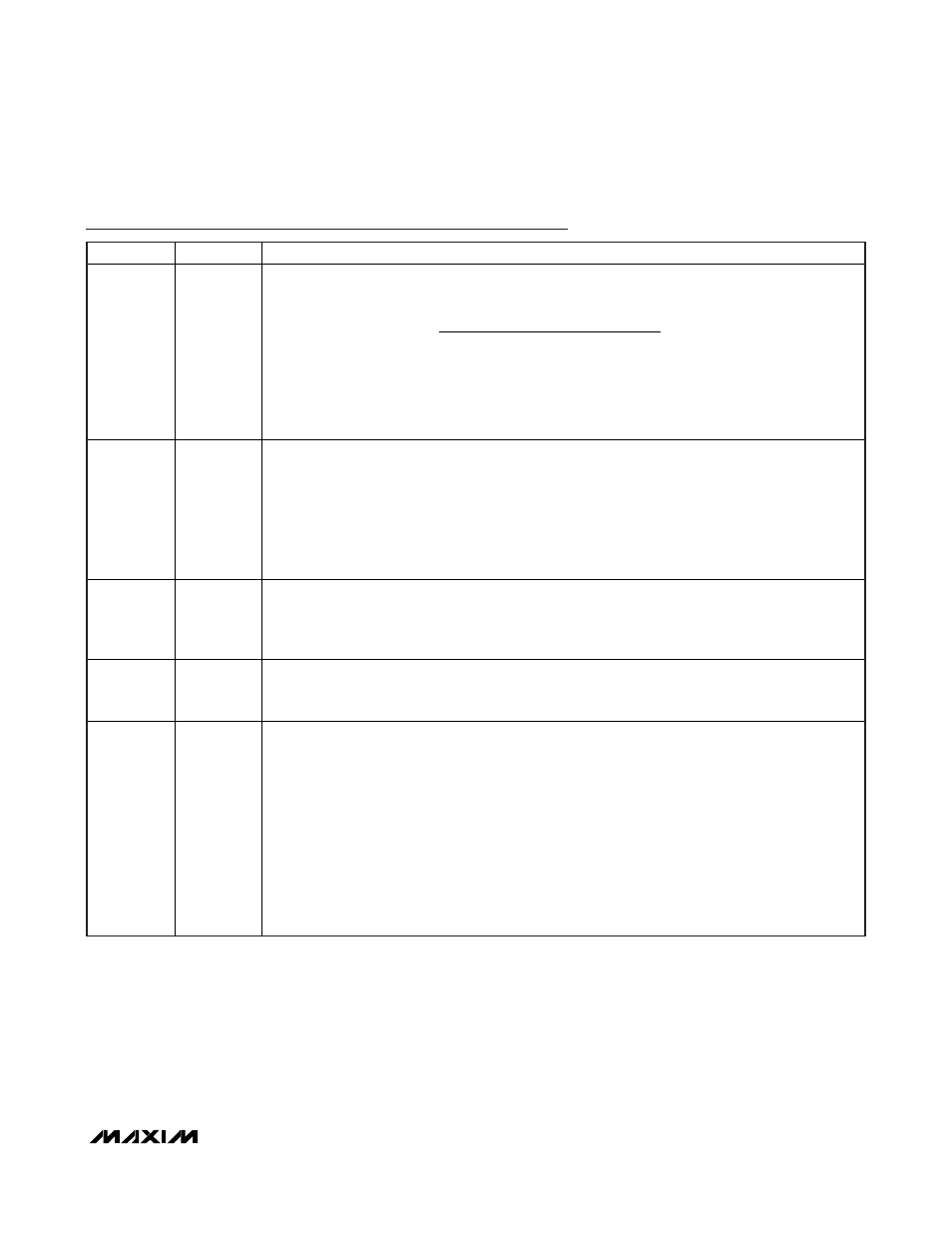

Pin Description (continued)

PIN

NAME

FUNCTION

15 FBAC2

Output of the Voltage-Positioning Transconductance Amplifier for SMPS2. The RC network between

this pin and the positive side of the remote-sensed output voltage sets the transient AC droop:

where R

DROOP_AC2

is the transient (AC) voltage-positioning slope that provides an acceptable

trade-off between stability and load-transient response, G

m(FBAC2)

= 2mS (typ), and R

SENSE2

is the

value of the current-sense element that is used to provide the (CSP2, CSN2) current-sense voltage,

Z

CFB2

is the impedance of C

FB2

, and FBAC2 is high impedance in shutdown.

16 FBDC2

Feedback-Sense Input for SMPS2. Connect a resistor R

FBDC2

between FBDC2 and the positive side

of the feedback remote sense, and a capacitor from FBAC2 to couple the AC ripple from FBAC2 to

FBDC2. An integrator on FBDC2 corrects for output ripple and ground-sense offset.

To enable a DC load-line less than the AC load-line, add a resistor from FBAC2 to FBDC2.

To enable a DC load-line equal to the AC load-line, short FBAC2 to FBDC2. See the Core Steady-

State Voltage Positioning (DC Droop) section.

FBDC2 is high impedance in shutdown.

17 CSN2

Negative Current-Sense Input for SMPS2. Connect to the negative side of the output current-sensing

resistor or the filtering capacitor if the DC resistance of the output inductor is utilized for current

sensing.

A 20

discharge FET is enabled from CSN2 to PGND when the SMPS2 is shut down.

18 CSP2

Positive Current-Sense Input for SMPS2. Connect to the positive side of the output current-sensing

resistor or the filtering capacitor if the DC resistance of the output inductor is utilized for current

sensing.

19 PGD_IN

System Power-Good Input

PGD_IN is low when

SHDN first goes high. The MAX17480 decodes the two SVI bits to determine

the boot voltage. The SVI bits can be changed dynamically during this time while PGD_IN remains

low and PWRGD is still low.

PGD_IN goes high after the MAX17480 reaches the boot voltage. This indicates that the SVI block

is active, and the MAX17480 starts to respond to the SVI commands. The MAX17480 stores the

boot VID when PWRGD first goes high. The stored boot VID is cleared by rising

SHDN.

After PGD_IN has gone high, if at any time PGD_IN goes low, the MAX17480 regulates to the

previously stored boot VID. The slew rate during this transition is set by the resistor between the

TIME and GND pins. PWRGD follows the blanking for normal VID transition.

The subsequent rising edge of PGD_IN does not change the stored VID.

R

R

R

R

R

R

DROOP AC

FBAC

FBDC

FBAC

FBDC

FB

_

2

2

2

2

2

2

=

×

+

+

Z

Z

R

G

CFB

SENSE

m FBAC

2

2

2

Ч

Ч

(

)