Pin description – Rainbow Electronics MAX17480 User Manual

Page 16

MAX17480

AMD 2-/3-Output Mobile Serial

VID Controller

16

______________________________________________________________________________________

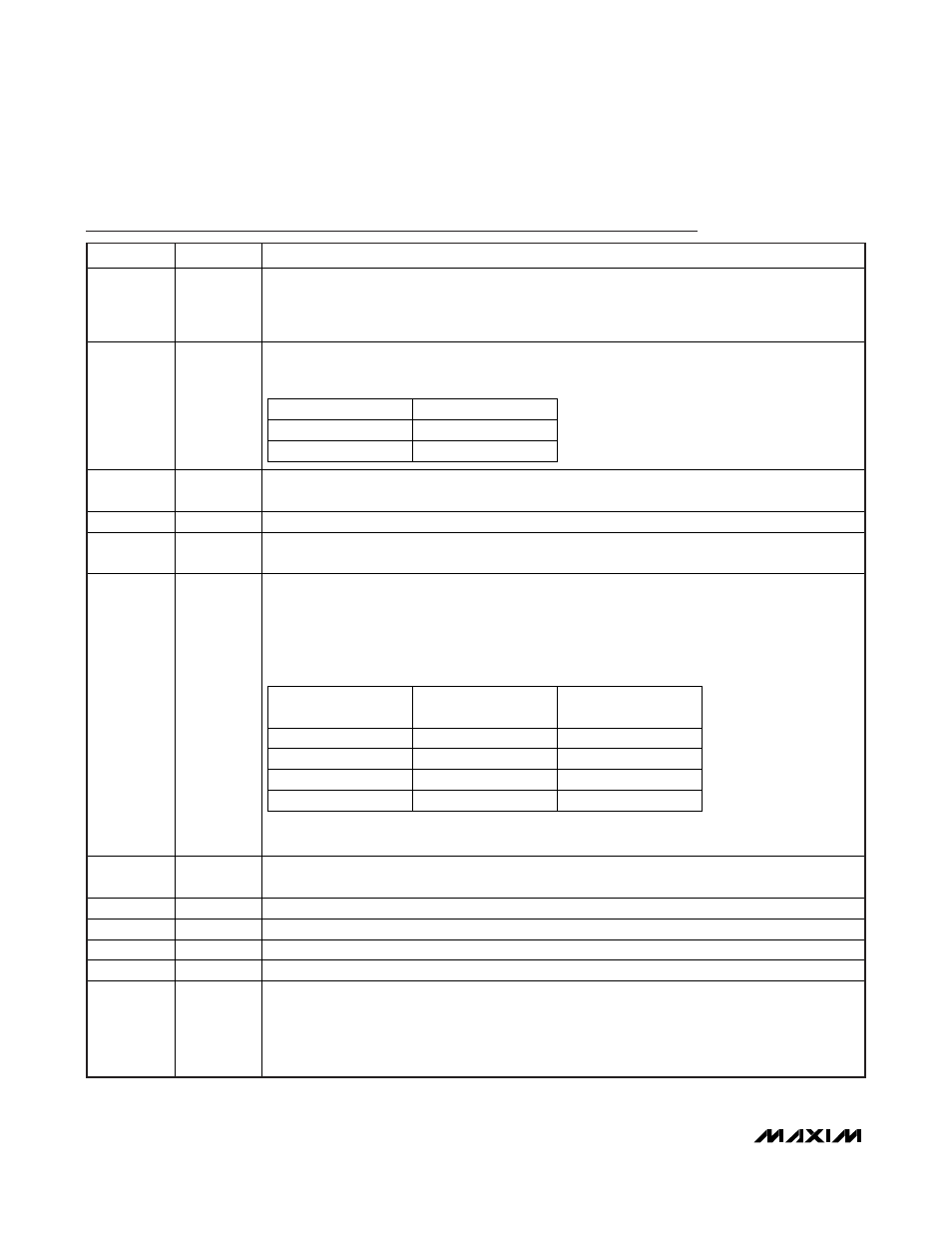

Pin Description

PIN

NAME

FUNCTION

1 ILIM12

SMPS1 and SMPS2 Current-Limit Adjust Input. The positive current-limit threshold voltage is 0.052

times the voltage between TIME and ILIM over a 0.2V to 1.0V range of V(TIME, ILIM). The I

MIN12

minimum current-limit threshold voltage in skip mode is precisely 15% of the corresponding

positive current-limit threshold voltage.

2 ILIM3

SMPS3 Current-Limit Adjust Input. Two-level current-limit setting for SMPS3. The I

LX3MIN

minimum

current-limit threshold in skip mode is precisely 25% of the corresponding positive current-limit

threshold.

ILIM3

I

LX3PK

(A)

V

CC

5.25

GND 4.25

3, 4

IN3

Internal High-Side MOSFET Drain Connection for SMPS3. Bypass to PGND with a 10µF or greater

ceramic capacitor close to the IC.

5, 6

LX3

Inductor Connection for SMPS3. Connect LX3 to the switched side of the inductor.

7 BST3

Boost Flying Capacitor Connection for SMPS3. An internal switch between V

DD

and BST3 charges

the flying capacitor during the time the low-side FET is on.

8

SHDN

Active-Low Shutdown Control Input. This input cannot withstand the battery voltage. Connect to

V

CC

for normal operation. Connect to ground to put the IC into its 1µA max shutdown state. During

startup, the output voltage is ramped up to the voltage set by the SVC and SVD inputs at a slew rate

of 1mV/µs. In shutdown, the outputs are discharged using a 20

switch through the CSN_ pins for

the core SMPSs and through the OUT3 pin for the northbridge SMPS.

The MAX17480 powers up to the voltage set by the two SVI bits.

SVC

SVD

BOOT VOLTAGE

V

OUT

(V)

0 0 1.1

0 1 1.0

1 0 0.9

1 1 0.8

The MAX17480 stores the boot VID when PWRGD first goes high. The stored boot VID is cleared

by a rising

SHDN signal.

9 OUT3

Feedback Input for SMPS3. A 20

discharge FET is enabled from OUT3 to PGND when SMPS3 is

shut down.

10 AGND

Analog

Ground

11

SVD

Serial VID Data

12

SVC

Serial VID Clock

13 V

DDIO

CPU I/O Voltage (1.8V or 1.5V). Logic thresholds for SVD and SVC are relative to the voltage at V

DDIO

.

14 GNDS2

SMPS2 Remote Ground-Sense Input. Normally connected to GND directly at the load. GNDS2

internally connects to a transconductance amplifier that fine tunes the output voltage—

compensating for voltage drops from the SMPS ground to the load ground.

Connect GNDS1 or GNDS2 above 0.9V combined-mode operation (unified core). When GNDS2 is

pulled above 0.9V, GNDS1 is used as the remote ground-sense input.