Smps applications information – Rainbow Electronics MAX17480 User Manual

Page 45

MAX17480

AMD 2-/3-Output Mobile Serial

VID Controller

______________________________________________________________________________________

45

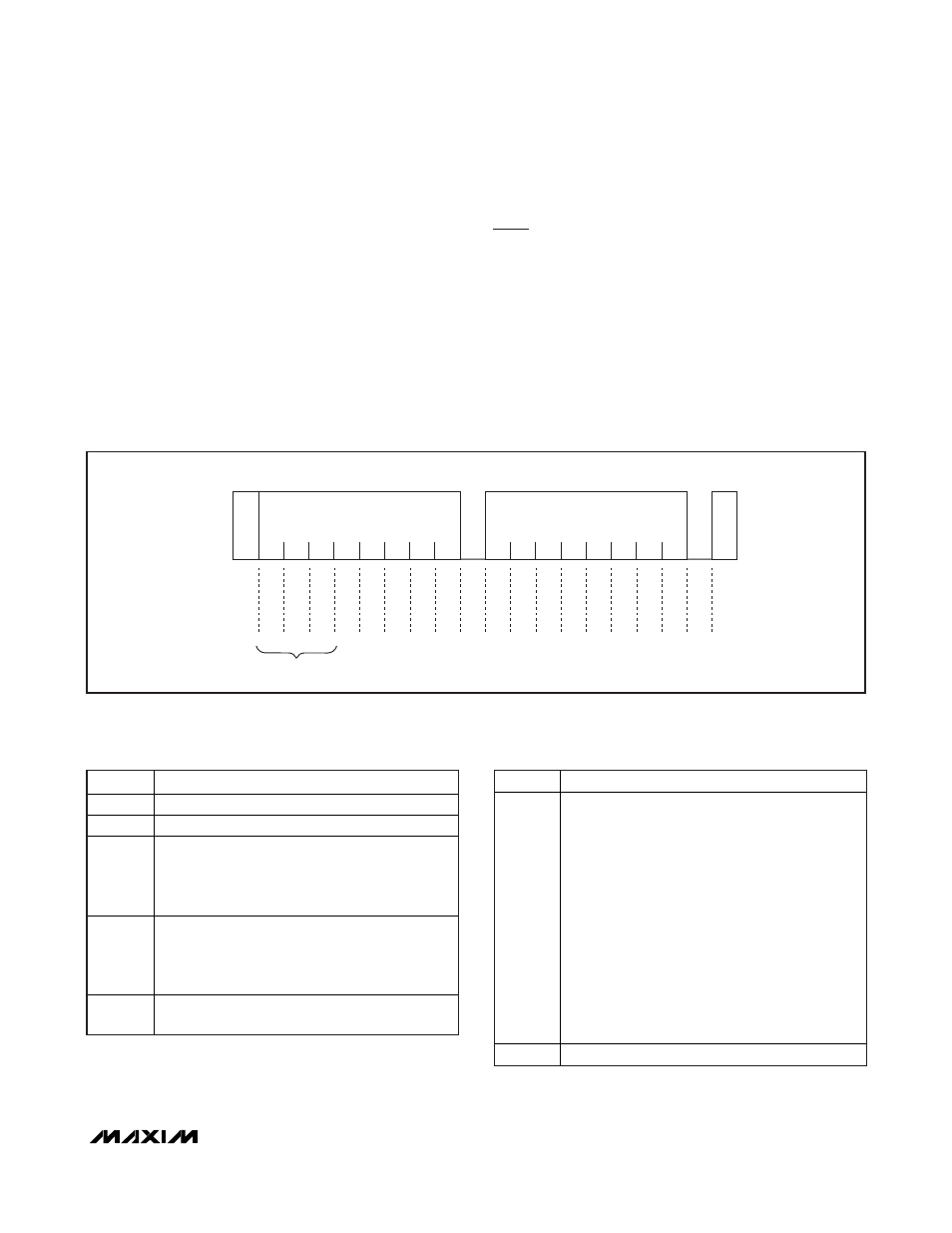

Command Byte

A complete command consists of a START condition

(S) followed by the MAX17480’s slave address and a

data phase, followed by a STOP condition (P). For the

slave address, bits 6:4 are always 110 and bit 3 is X

(don’t care). The WR bit should always be 1 since read

functions are not supported. Figure 14 is the SVI bus

data-transfer summary. Table 7 is a description of the

SVI send byte address and Table 8 describes serial

VID 8-bit field encoding.

SMPS Applications Information

Duty-Cycle Limits

Minimum Input Voltage

The minimum input operating voltage (dropout voltage)

is restricted by stability requirements, not the minimum

off-time (t

OFF(MIN)

). The MAX17480 does not include

slope compensation, so the controller becomes unsta-

ble with duty cycles greater than 50% per phase:

V

IN(MIN)

≥ 2V

OUT(MAX)

However, the controller can briefly operate with duty

cycles over 50% during heavy load transients.

Table 7. SVI Send Byte Address Description

Table 8. Serial VID 8-Bit Field Encoding

BIT

DESCRIPTION

6:4 Always

110b.

3 X—don’t

care.

2

VDD1, if set then the following data byte

contains the VID for VDD1. Bit 2 is ignored in

combined mode (GNDS1 or GNDS2 = V

DDIO

).

VDD1 refers to CORE1 of the AMD CPU.

1

VDD0, if set then the following data byte

contains the VID for VDD0 in separate mode, and

the unified VDD in combined mode. VDD0 refers

to CORE0 of the AMD CPU.

0

VDDNB, if set then the following data byte

contains the VID for VDDNB.

BIT

DESCRIPTION

7

PSI_L: Power-Save Indicator

0 means the processor is at an optimal load and

the SMPS(s) can enter power-saving mode. The

SMPS operates in pulse-skipping mode after

exiting the boot mode. Offset is disabled if

previously enabled by the OPTION pin. The

MAX17480 enters 1-phase operation if in

combined mode (GNDS1 or GNDS2 = H).

1 means the processor is in a high current-

consumption state. The SMPS operates in forced-

PWM mode after exiting the boot mode. Offset is

enabled if previously enabled by the OPTION

pin. The MAX17480 returns to 2-phase operation

if in combined mode (GNDS1 or GNDS2 = H).

6:0

SVID[6:0] as defined in Table 7.

Figure 14. SVI Bus Data Transfer Summary

SET DAC AND PSI_L

SLAVE ADDRESS

S

P

STOP

START

PSI_L

BIT6

1

1

0

X

NB

WR (WRITE) = 0

ACK

VDD1 (CORE1)

VDD0 (CORE0)

FIXED VALUES

BIT0

BIT5

BIT4

BIT3

BIT2

BIT1

ACK