Table 3. boot voltage code table – Rainbow Electronics MAX17480 User Manual

Page 28

MAX17480

AMD 2-/3-Output Mobile Serial

VID Controller

28

______________________________________________________________________________________

Nominal Output-Voltage Selection

Core SMPS Output Voltage

The nominal no-load output voltage (V

TARGET

) for each

SMPS is defined by the selected voltage reference (VID

DAC) plus the remote ground-sense adjustment

(V

GNDS

) and the offset voltage (V

OFFSET

) as defined in

the following equation:

where V

DAC

is the selected VID voltage of the core

SMPS DAC, V

GNDS

is the ground-sense correction volt-

age for core supplies, and V

OFFSET

is the +12.5mV off-

set enabled by the OPTION pin when the PSI_L is set

high for core supplies.

NB SMPS Output Voltage

The nominal output voltage (V

TARGET

) for the NB is

defined by the selected voltage reference (VID DAC)

plus the offset voltage (V

OFFSET_NB

) as defined in the

following equation:

where V

DAC

is the selected VID voltage of the NB DAC,

and V

OFFSET_NB

is +12.5mV.

7-Bit DAC

Inside the MAX17480 are three 7-bit digital-to-analog

converters (DACs). Each DAC can be individually pro-

grammed to different voltage levels by the serial-inter-

face bus. The DAC sets the target for the output voltage

for the core and NB SMPSs. The available DAC codes

and resulting output voltages are compatible with the

AMD SVI (Table 4) specifications.

Boot Voltage

On startup, the MAX17480 slews the target for all three

DACs from ground to the boot voltage set by the SVC

and SVD pin-voltage levels. While the output is still below

regulation, the SVC and SVD levels can be changed,

and the MAX17480 sets the DACs to the new boot volt-

age. Once the programmed boot voltage is reached and

PWRGD goes high, the MAX17480 stores the boot VID.

Changes in the SVC and SVD settings do not change the

output voltage once the boot VID is stored. When

PGD_IN goes high, the MAX17480 exits boot mode, and

the three DACs can be independently set to any voltage

in the VID table by the serial interface.

If PGD_IN goes from high to low any time after the boot

VID is stored, the MAX17480 sets all three DACs back

to the voltage of the stored boot VID.

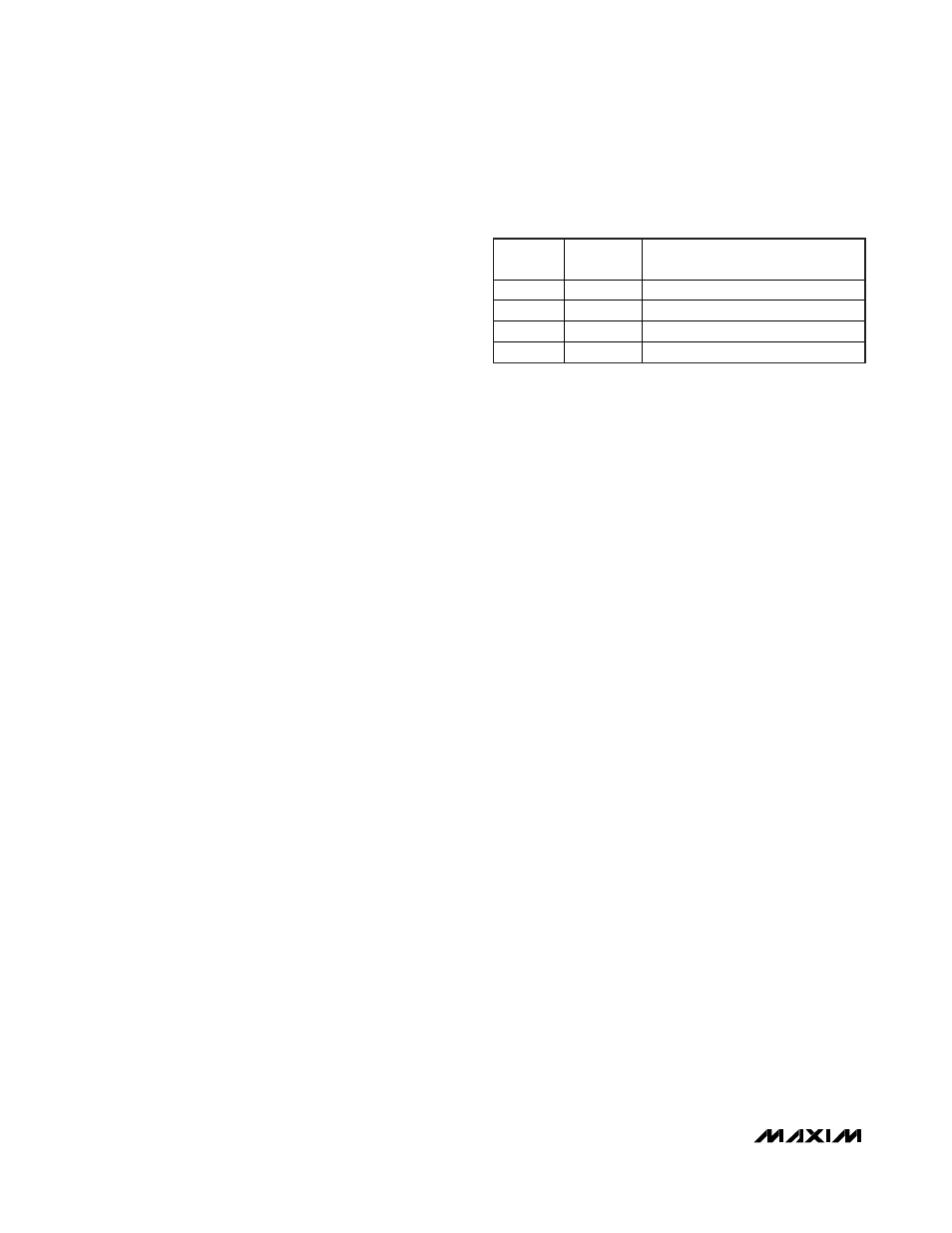

Table 3 is the boot voltage code table.

Core SMPS Offset

A +12.5mV offset can be added to both core SMPS

DAC voltages for applications that include DC droop.

The offset is applied only after the MAX17480 exits boot

mode (PGD_IN going from low to high), and the

MAX17480 enters the serial-interface mode. The offset

is disabled when the PSI_L bit is set, saving more

power when the load is light.

The OPTION pin setting enables or disables the

+12.5mV offset. Connect OPTION to OSC (2V) or GND

to enable the offset. Keep OPTION connected to 3.3V

or V

CC

to disable the offset. See the

Offset and

Address Change for Core SMPSs (OPTION)

section.

NB SMPS Offset

The NB SMPS output has a -5.5mV/A load line. A

+12.5mV offset is added to keep the output within regu-

lation over the full load. See the

Offset and Current-

Limit Setting for NB SMPS (ILIM3)

section.

Output-Voltage Transition Timing

SMPS Output-Voltage Transition

The MAX17480 performs positive voltage transitions in

a controlled manner, automatically minimizing input

surge currents. This feature allows the circuit designer

to achieve nearly ideal transitions, guaranteeing just-in-

time arrival at the new output-voltage level with the low-

est possible peak currents for a given output

capacitance. The slew rate (set by resistor R

TIME

) must

be set fast enough to ensure that the transition is com-

pleted within the maximum allotted time for proper CPU

operation. R

TIME

is between 35.7k

Ω and 357kΩ for cor-

responding slew rates between 25mV/µs to 2.5mV/µs,

respectively, for the SMPSs.

At the beginning of an output-voltage transition, the

MAX17480 blanks both PWRGD comparator thresholds,

preventing the PWRGD open-drain output from chang-

ing states during the transition. At the end of an upward

VID transition, the controller enables both PWRGD

thresholds approximately 20µs after the slew-rate

controller reaches the target output voltage. At the end

V

V

V

V

TARGET

OUT

DAC

OFFSET NB

3

3

=

=

+

_

V

V

V

V

V

TARGET

FBDC

DAC

GNDS

OFFSET

=

=

+

+

SVC

SVD

BOOT VOLTAGE

V

OUT

(V)

0 0

1.1

0 1

1.0

1 0

0.9

1 1

0.8

Table 3. Boot Voltage Code Table