Rainbow Electronics MAX17480 User Manual

Page 26

MAX17480

AMD 2-/3-Output Mobile Serial

VID Controller

26

______________________________________________________________________________________

Transient Phase Repeat

When a transient occurs, the output voltage deviation

depends on the controller’s ability to quickly detect the

transient and slew the inductor current. A fixed-frequency

controller typically responds only when a clock edge

occurs, resulting in a delayed transient response. To

minimize this delay time, the MAX17480 includes

enhanced transient detection and transient phase

repeat capabilities. If the controller detects that the out-

put voltage has dropped by 41mV, the transient detec-

tion comparator immediately retriggers the phase that

completed its on-time last. The controller triggers the

subsequent phases as normal, on the appropriate

oscillator edges. This effectively triggers a phase a full

cycle early, increasing the total inductor-current slew

rate and providing an immediate transient response.

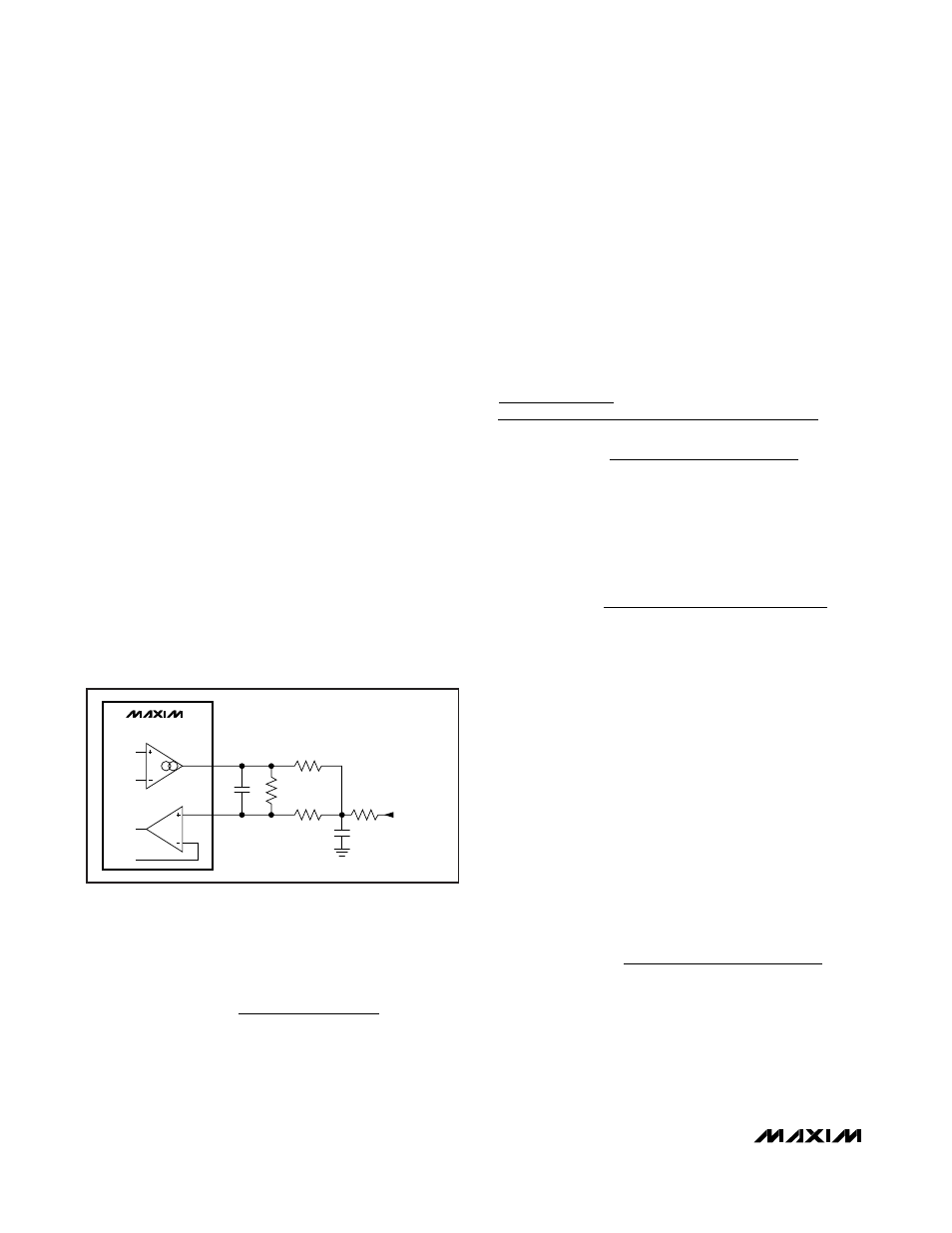

Core SMPS Feedback

Adjustment Amplifiers

The MAX17480 provides an FBAC and FBDC pin for

each SMPS to allow for flexible AC and DC droop set-

tings. FBAC is the output of an internal transconduc-

tance amplifier that outputs a current proportional to the

current-sense signal. FBDC is the feedback input that is

compared against the internal target. Place resistors

and capacitors at the FBAC and FBDC pins as shown

in Figure 5. With this configuration, the DC droop is

always less than or equal to the AC droop.

Core Steady-State Voltage Positioning (DC Droop)

FBDC is the feedback input to the error amplifier.

Based on the configuration in Figure 5, the core SMPS

output voltage is given by:

where the target voltage (V

TARGET

) is defined in the

Nominal Output-Voltage Selection

section, and the

FBAC amplifier’s output current (I

FBAC

) is determined

by each phase’s current-sense voltage:

where V

CS

= V

CSP

- V

CSN

is the differential current-sense

voltage, and G

m(FBAC)

is typically 2mS as defined in the

Electrical Characteristics

table. DC droop is typically used

together with the +12.5mV offset feature to keep within the

DC tolerance window of the application. See the

Offset

and Address Change for Core SMPSs (OPTION)

section.

The ripple voltage on FBDC must be less than the -33mV

(max) transient phase repeat threshold:

where

∆I

L

is the inductor ripple current, R

ESR

is the

effective output ESR at the remote sense point, R

SENSE

is the current-sense element, and G

m(FBAC)

is 2.06mS

(max) as defined in the

Electrical Characteristics

table.

The worst-case inductor ripple occurs at the maximum

input-voltage and maximum output-voltage conditions:

To make the DC and AC load-lines the same, directly

short FBAC to FBDC.

To disable DC voltage positioning, remove R

FB

, which

connects FBAC to FBDC.

Core Transient Voltage-Positioning Amplifier

(AC Droop)

Each of the MAX17480 core supply SMPSs includes one

transconductance amplifier for voltage positioning. The

amplifiers’ inputs are generated by summing their respec-

tive current-sense inputs, which differentially sense the

voltage across either current-sense resistor or the induc-

tor’s DCR.

The voltage-positioning droop amplifier’s output (FBAC)

connects to the remote-sense point of the output

through an RC network that sets each phase’s AC volt-

age-positioning gain:

where the target voltage (V

TARGET

) is defined in the

Nominal Output-Voltage Selection

section, Z

CFB

is the

effective impedance of C

FB

, and the FBAC amplifier’s

output current (I

FBAC

) is determined by each phase’s

current-sense voltage:

V

V

R

R

R

R

R

Z

OUT

TARGET

FBAC

FBDC

FBAC

FBDC

FB

CF

=

−

×

+

+

B

B

FBDC

I

∆I

V

V

V

V

L MAX

OUT MAX

IN MAX

OUT MAX

IN M

(

)

(

)

(

)

(

)

(

=

−

(

)

A

AX SW

f

L

)

∆

R

mV

I R

R

R

FBDC

L ESR

FBAC

F

66

≤

−

(

)

+

(

B

B

FBAC

L SENSE m FBAC

R

I R

G

mV

)

(

)

∆

− 66

R

R

R

R

I R

G

R

FBAC

FBAC

FBDC

FB

L SENSE m FBAC

FBDC

+

+

+

∆

(

)

∆∆I R

mV

L ESR

2

33

≤

I

G

V

FBAC

m FBAC

CS

=

(

)

V

V

R

R

R

R

R

I

OUT

TARGET

FBDC

FBAC

FBAC

FBDC

FB

FB

=

−

Ч

+

+

Ч

A

AC

R

FBAC

R

FBDC

FBAC

CSP

CSN

G

m(FBAC)

ERROR

AMP

FBDC

C

FB

4700pF

CORE SENSE_H

AGND

100

Ω

TARGET

R

FB

MAX17480

Figure 5. Core SMPS Feedback Connection