Shutdown, Vrhot temperature comparator – Rainbow Electronics MAX17480 User Manual

Page 35

MAX17480

AMD 2-/3-Output Mobile Serial

VID Controller

______________________________________________________________________________________

35

Shutdown

When SHDN goes low, the MAX17480 enters shutdown

mode. PWRGD is pulled low immediately and forces all

DH and DL low, and all three outputs are discharged

through the 20

Ω internal discharge FETs through the CSN

pin for core SMPSs and through the OUT3 pin for NB

SMPSs.

VRHOT Temperature Comparator

The MAX17480 features an independent comparator with

an accurate threshold (V

HOT

) that tracks the analog sup-

ply voltage (V

HOT

= 0.3V

CC

). Use a resistor- and thermis-

tor-divider between V

CC

and GND to generate a

voltage-SMPS overtemperature monitor. Place the thermis-

tor as close as possible to the MOSFETs and inductors.

Place three individual thermistors near to each SMPS to

monitor the temperature of the respective SMPS. When

core SMPSs are in combined-mode operation, the cur-

rent-balance circuit balances the currents between

core SMPS phases. As such, the power loss and heat

in each phase should be identical, apart from the

effects of placement and airflow over each phase.

Single thermistors can be placed near either of the

phases and still be effective for core SMPS temperature

monitoring, and one thermistor can be saved. See

Figure 10.

MAX17480

V

CC

THRM

R

THRM

R

NTC

GND

PLACE R

NTC

NEXT TO THE

HOTTEST POWER COMPONENT.

MAX17480

V

CC

THRM

R

PTC2

R

THRM

GND

PLACE R

PTC1

, R

PTC2

, AND R

PTC3

NEXT TO THE RESPECTIVE SMPS'S

POWER COMPONENT.

R

PTC1

R

PTC3

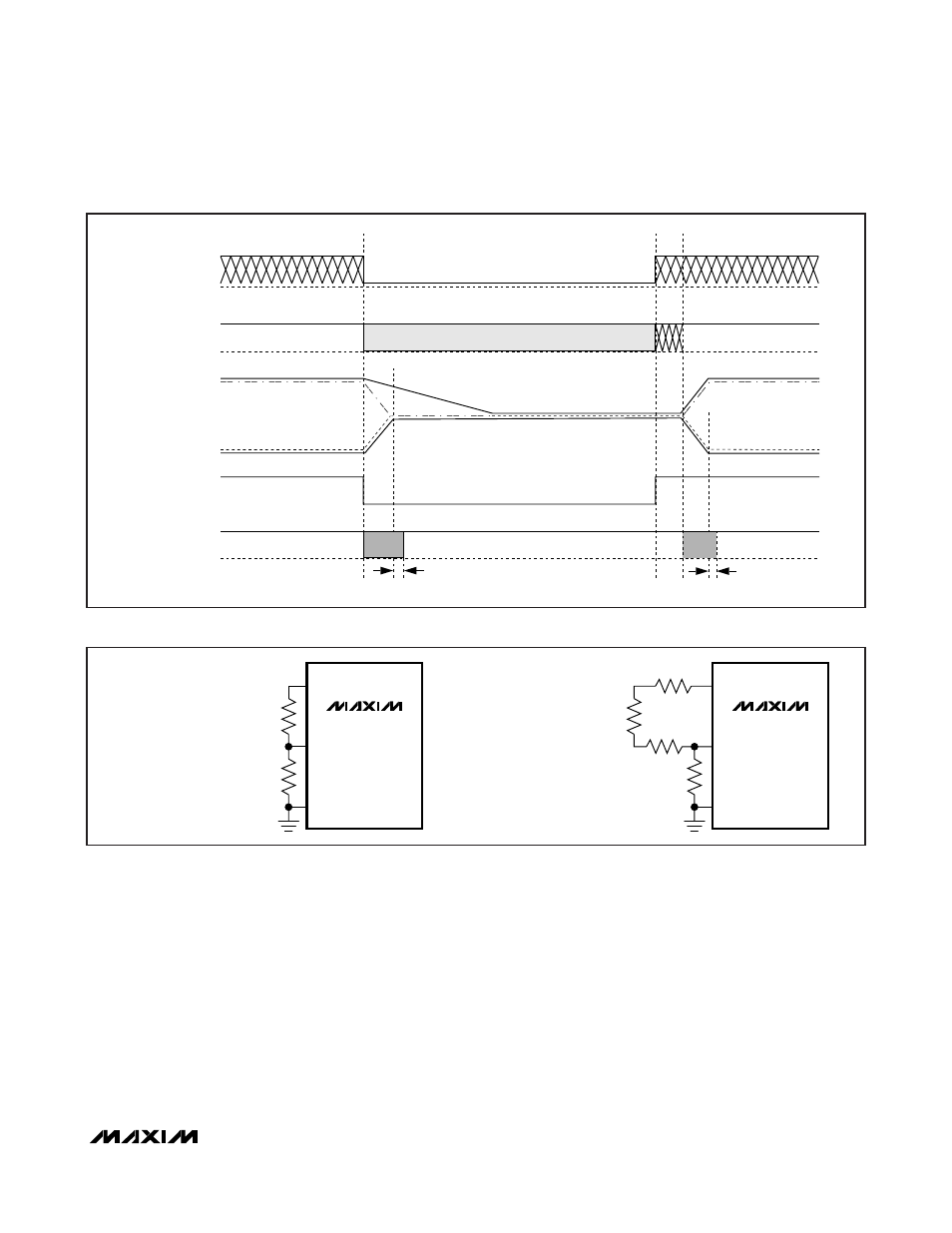

Figure 10. THRM Configuration

20

µs

20

µs

2-BIT BOOT VID, SVC/SVD INPUTS DISABLED

PSI_L

PGD_IN

PWRGD

SMPS V

OUT

(HIGH DAC TARGET)

(LOW DAC TARGET)

SMPS V

OUT

SVC/SVD

BUS IDLE

BUS IDLE

PULSE-SKIPPING MODE

TARGET

V

OUT

BLANK

HIGH-Z

BLANK

HIGH-Z

Figure 9. PGD_IN Timing