Page head, Page head clock and synchronization in system 6000 – TC Electronic Broadcast 6000 User Manual

Page 59

59

paGe Head

in dept

H

59

paGe Head

ClOCK and synCHrOnIzaTIOn In sysTem 6000

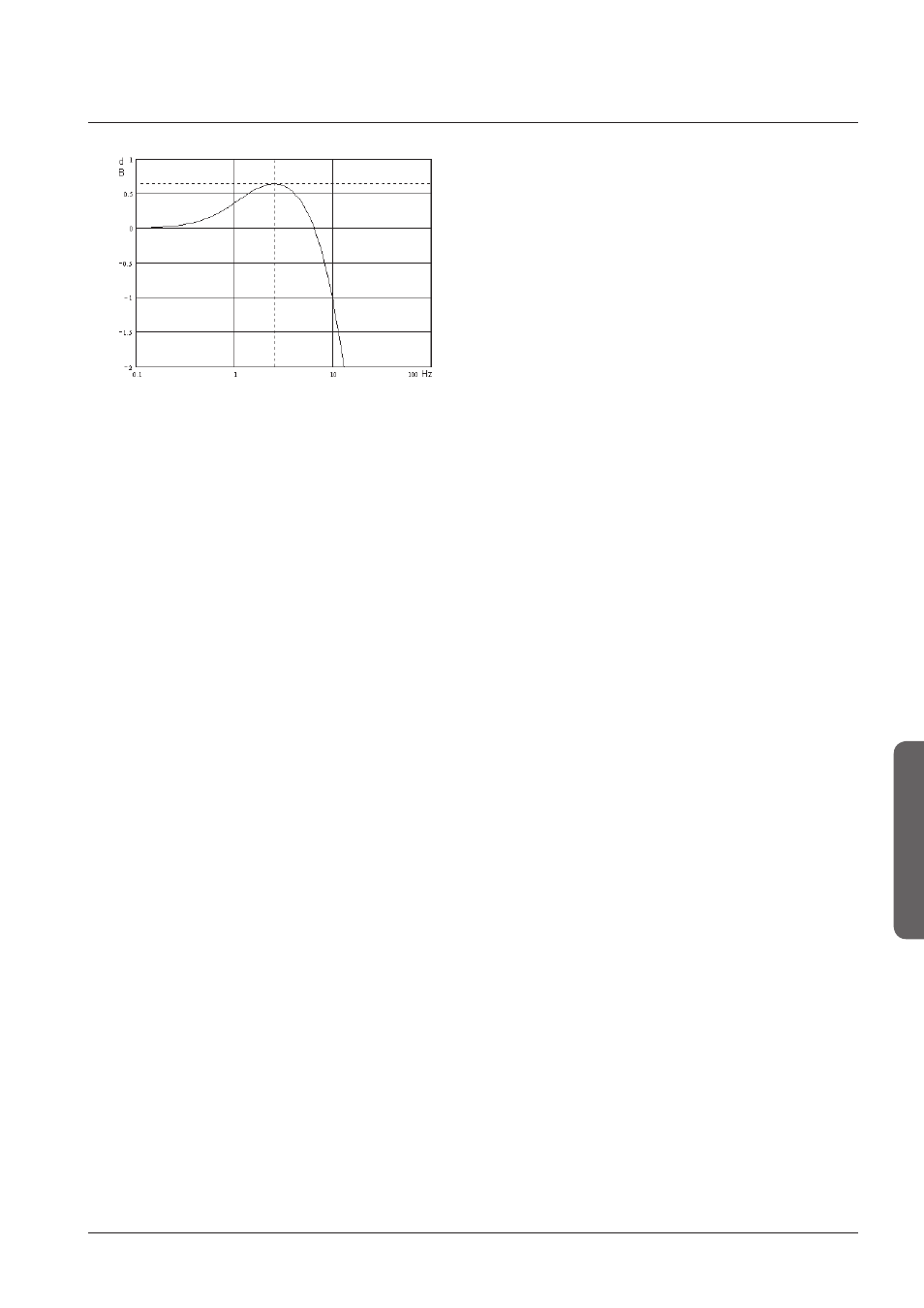

Figure 5 Zoomed picture of the jitter rejection filter.

Lock range

There are some devices on the market that feature jitter

rejection to some extent but most of them uses a common

technology (VCXO type of oscillator in the PLL). This

technology is limited in the terms of lock range. This

means that the jitter rejection only can be done at the

known frequencies e.g. 96 kHz, 88.2 kHz, 48 kHz +/- a

few hundred PPM. This is typically enough given the fact

that most clock oscillators have a precision of less than +/-

50ppm but if you want to use other sample rates (e.g. vary

speed or the broadcast related 44.056 kHz) you will have

to do without the jitter rejection.

System 6000 uses a special technology that makes it able

to lock to all sample rates from: 30 to 34 kHz, 42.5 to 45.6

kHz, 46.5 to 48.5 kHz, 85 to 91 kHz and 93 to 97 kHz. This

means that every signal at sample rates in these ranges

will be treated with the same jitter rejection filter. The

performance is not only good in a narrow range around

one or two sample rates.

Intrinsic jitter

The intrinsic sampling jitter on System 6000 has been

optimized through a long period of trimming in order to

make the perfect AD- and DA-conversion on the ADA24/96

card. This is also why the intrinsic interface jitter is as low

as < 1 ns peak, BW: 700 to 100 kHz that makes the perfect

starting point for the digital setup.

System 6000 technical specifications

regarding the clock circuitry:

Jitter rejection filter (4’Th order filter): < -3dB @ 50 Hz

< -69dB @ 500 Hz

< -100dB @ 1.4 kHz

Jitter gain:

< 1 dB @ 2Hz

Jitter rejection at

external sample rates:

30 to 34 kHz,

42.5 to 45.6 kHz,

46.5 to 48.5 kHz,

85 to 91 kHz,

93 to 97 kHz.

Internal sample rates:

96 kHz, 88.2 kHz,

48 kHz and 44.1kHz.

Internal clock precision:

+/- 30 PPM.

Intrinsic interface jitter:

< 1 ns peak,

BW: 700 to 100 Hz.