Figure 2-11, Board hardware – Xilinx ML310 User Manual

Page 37

ML310 User Guide

37

UG068 (v1.01) August 25, 2004

1-800-255-7778

Board Hardware

R

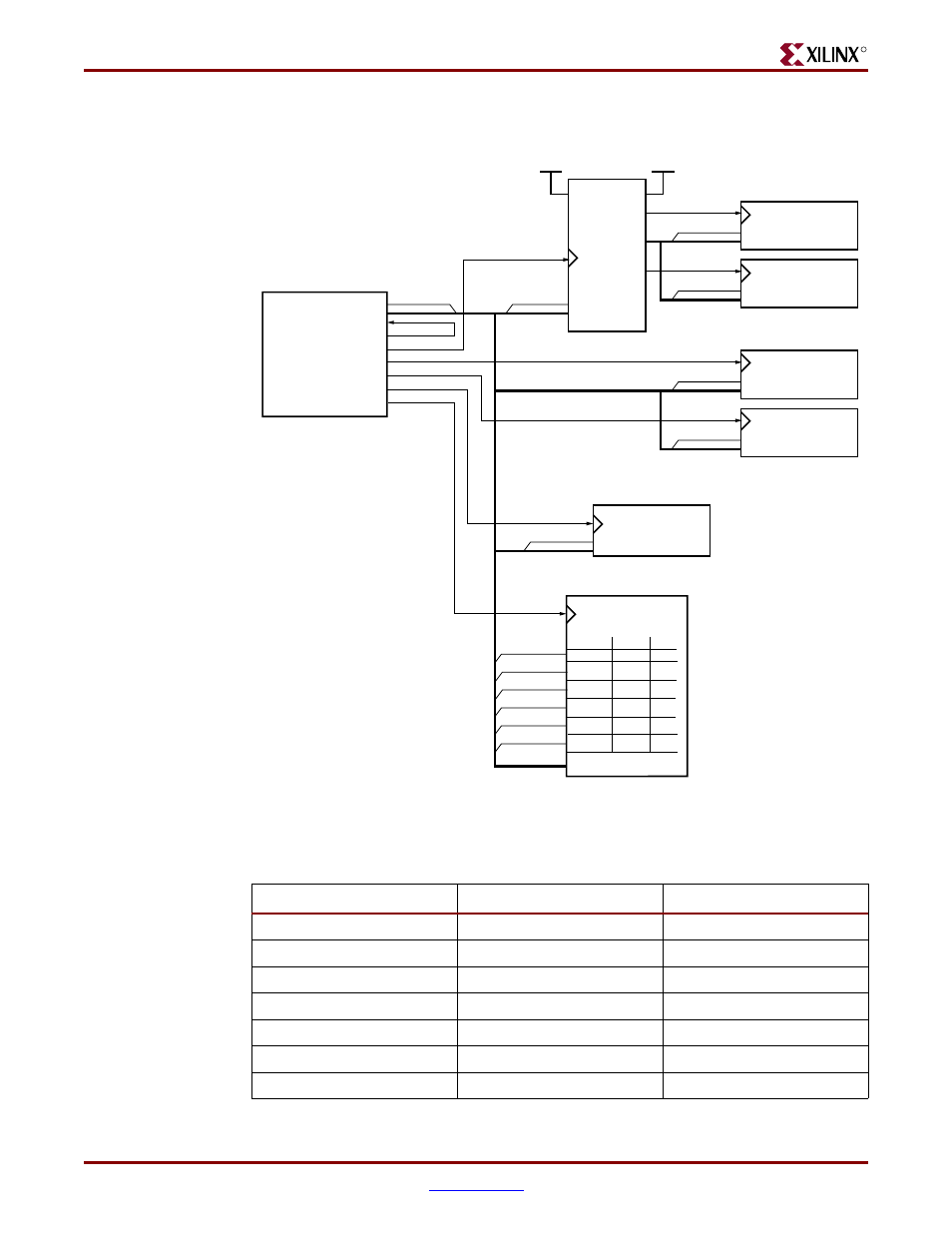

shows the connections for the PCI controller.

Figure 2-11:

PCI Bus and Device Connectivity

Table 2-10:

PCI Controller Connections

UCF Signal Name

XC2VP30 Pin (U37)

Description

PCI_CLK0

T2

PCI_P_CLK0

PCI_CLK1

R2

PCI_P_CLK1

PCI_CLK2

R5

PCI_P_CLK2

PCI_CLK3

R6

PCI_P_CLK3

PCI_CLK4

R3

PCI_P_CLK4

PCI_CLK5

R4

PCI_P_CLK5

PCI_CLK5_FB

C15

PCI_P_CLK5

PCI-to-PCI

Bridge TI2250

Intel 10/100

Ethernet NIC

5.0V PCI Slot 6

5.0V PCI Slot 4

Virtex-II Pro

FPGA

XC2VP30

ALi Southbridge

IDSEL

IDSEL

0xAC23 104C

0x1229 8086

0x5451 10B9

Dev ID Vend ID

IDSEL

0x1533 10B9

0x5457 10B9

0x5237 10B9

0x5229 10B9

0x5237 10B9

PCI_BUS

IDSEL

PCI_BUS

IDSEL

PCI_BUS

IDSEL

PCI_BUS

IDSEL

PCI_BUS

IDSEL

PCI_BUS

USB#1

PCI_BUS

PCI Bus

PCI_S_AD18

PCI_S_CLK0

PCI_S_AD19

PCI_P_AD25

PCI_P_AD24

3.3V

PCI_P_CLK5

PCI_P_CLK4

PCI_P_CLK0

PCI_P_CLK1

PCI_P_CLK2

PCI_P_CLK3

PCI_S_CLK1

3.3V PCI Slot 5

3.3V PCI Slot 3

PCI_P_AD21

PCI_P_AD22

PCI_P_AD23

PCI_P_AD31

IDE Bus

PCI_P_AD27

USB#2

PCI_P_AD26

Modem

PCI_P_AD19

S. Bridge

PCI_P_AD18

Audio

PCI_P_AD17

5.0V

U32

U37

U15

U11