Diagram, Figure 1 – Texas Instruments TMS320C642x DSP User Manual

Page 7

www.ti.com

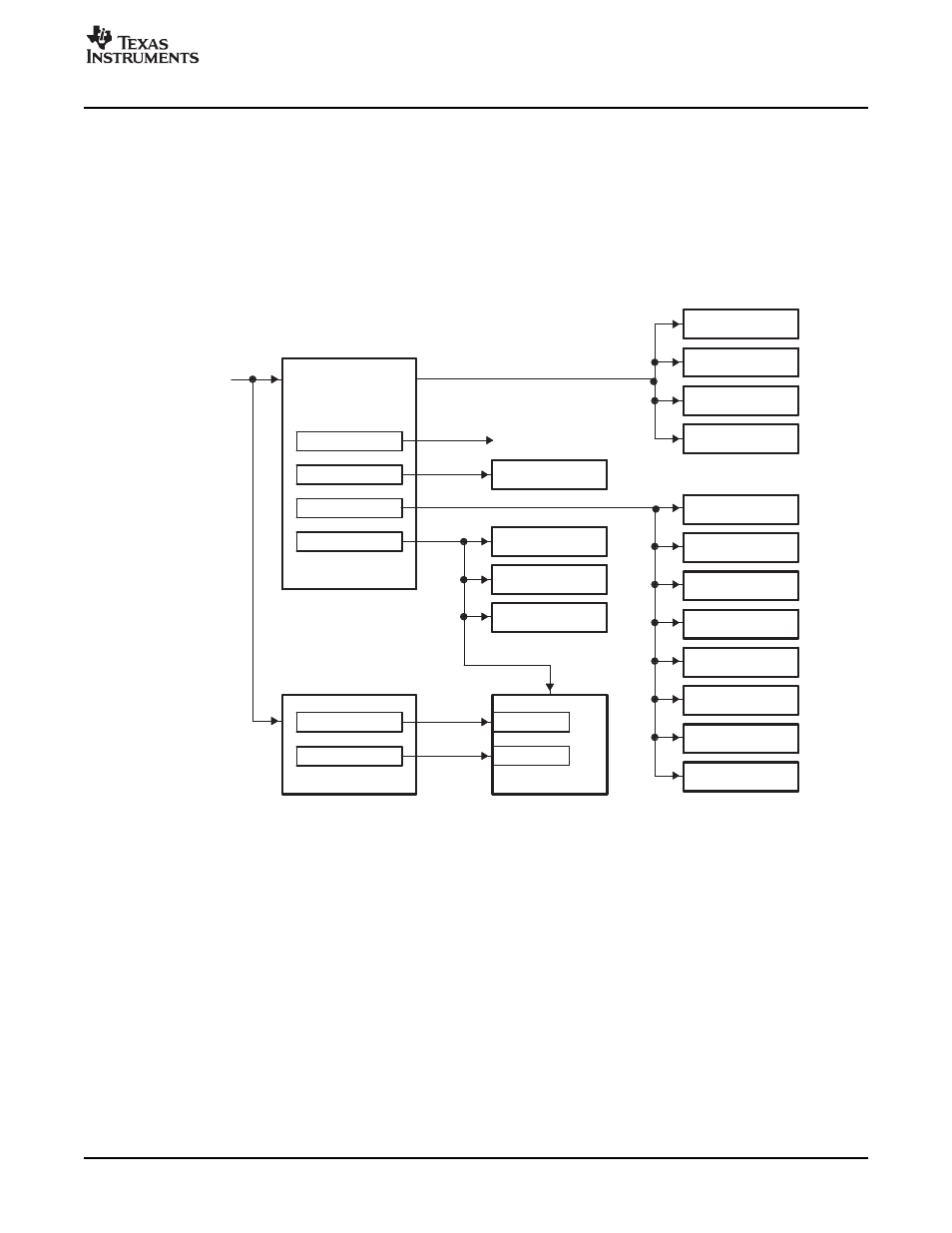

DSP Subsystem

SYSCLK1

SYSCLK3

SCR

EDMA

DDR2 PHY

DDR2 VTP

DDR2 Mem Ctlr

PLLDIV1 (/2)

BPDIV

PLL Controller 2

PLL Controller 1

PLLDIV2 (/3)

PLLDIV3 (/6)

PLLDIV1 (/1)

SYSCLK2

UARTs (x2)

I2C

Timers (x3)

PWMs (x3)

EMAC

EMIFA

VLYNQ

HPI

McASP0

McBSP0

GPIO

McBSP1

PCI

MXI/CLKIN

(15−30 MHz)

OSCDIV1 (/1)

OBSCLK

(CLKOUT0 Pin)

AUXCLK

Device Clocking

Modules in the CLKDIV6 domain (for example, CLKDIV6 domain peripherals) must run at 1/6 the DSP

frequency.

Modules in the CLKIN domain (for example, UART, Timer, I2C, PWM) run at the MXI/CLKIN frequency,

asynchronous to the DSP. There is no fixed ratio requirement between these peripherals frequencies and

the DSP frequency.

Refer to device-specific data manual for the core clock domain for each peripheral.

Figure 1. Overall Clocking Diagram

SPRUES0B – December 2007

Phase-Locked Loop Controller (PLLC)

7

- Digital Signal Processor SM320F2812-HT (153 pages)

- MSP430x1xx (440 pages)

- Laser And Motor Drives DRV8811EVM (13 pages)

- TMS320 DSP (88 pages)

- MSP430x11x1 (45 pages)

- TVP5154EVM (55 pages)

- TMS320DM646X DMSOC (64 pages)

- CC2511 (24 pages)

- SN65HVS880 (4 pages)

- TPS650231EVM (14 pages)

- TMS320TCI648x (256 pages)

- TSC2007EVM-PDK (16 pages)

- UCC38500EVM (16 pages)

- TMS320C6000 (62 pages)

- SCAU020 (21 pages)

- TPS40051 (17 pages)

- TNETE2201 (14 pages)

- TMS320C64x DSP (306 pages)

- UCC2891 (21 pages)

- TMS320C3x (757 pages)

- MSP430 (138 pages)

- TMS320C6712D (102 pages)

- MSP430x4xx (512 pages)

- TMS320C6454 (225 pages)

- SPRU938B (48 pages)

- TUSB3210 (22 pages)

- TMS320C6457 (43 pages)

- CC2530ZNP (3 pages)

- TMS320C6455 (50 pages)

- TSB12LV26 (91 pages)

- TMS320C6472 (2 pages)

- VLYNQ Port (49 pages)

- TMS380C26 (92 pages)

- MSP-FET430 (95 pages)

- TMS320TCI6486 (160 pages)

- TPS2330 (22 pages)

- DM648 DSP (47 pages)

- TMS320DM36X (134 pages)

- MSC1211 (35 pages)

- SPRAA56 (29 pages)

- DAC7741EVM (28 pages)

- CDCM7005 (34 pages)

- TMS370 (99 pages)

- Adpater (37 pages)

- TMS320C6452 DSP (46 pages)