10 pll controller command register (pllcmd), 11 pll controller status register (pllstat), Pllcmd) – Texas Instruments TMS320C642x DSP User Manual

Page 28: Pllstat), Descriptions, Section 2.4.10, Section 2.4.11

www.ti.com

2.4.10

PLL Controller Command Register (PLLCMD)

2.4.11

PLL Controller Status Register (PLLSTAT)

PLL Controller

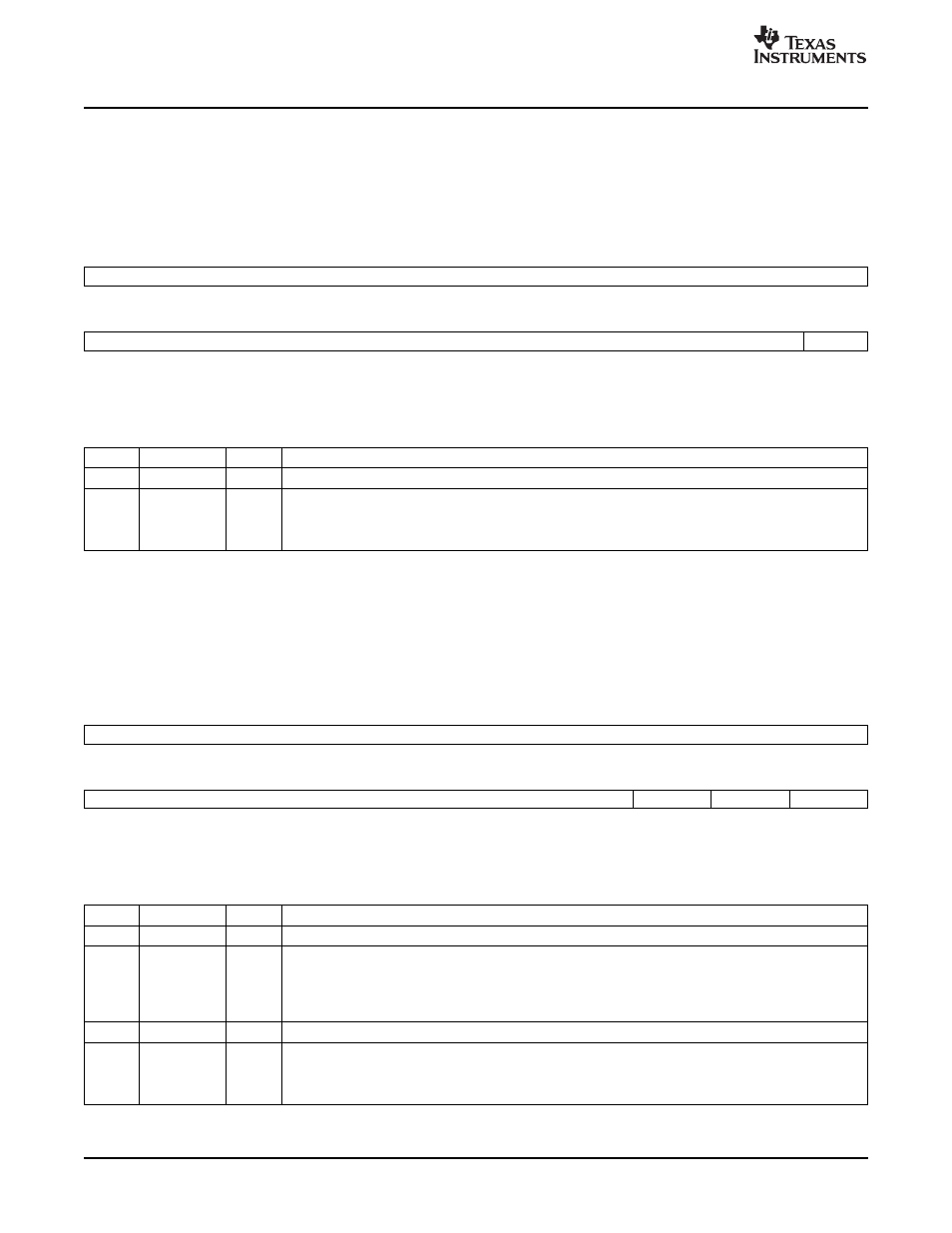

The PLL controller command register (PLLCMD) is shown in

and described in

PLLCMD contains the command bit for the GO operation. Writes of 1 initiate command. Writes of 0 clear

the bit, but have no effect.

Figure 13. PLL Controller Command Register (PLLCMD)

31

16

Reserved

R-0

15

1

0

Reserved

GOSET

R-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 19. PLL Controller Command Register (PLLCMD) Field Descriptions

Bit

Field

Value

Description

31-1

Reserved

0

Reserved

0

GOSET

GO bit for SYSCLKx loading new dividers and phase alignment.

0

Clear bit (no effect).

1

Initiate SYSCLKx phase alignment.

The PLL controller status register (PLLSTAT) is shown in

and described in

Figure 14. PLL Controller Status Register (PLLSTAT)

31

16

Reserved

R-0

15

3

2

1

0

Reserved

STABLE

Reserved

GOSTAT

R-0

R-0

R-0

R-0

LEGEND: R = Read only; -n = value after reset

Table 20. PLL Controller Status Register (PLLSTAT) Field Descriptions

Bit

Field

Value

Description

31-3

Reserved

0

Reserved

2

STABLE

OSC counter done, oscillator assumed to be stable. By the time the device comes out of reset, this bit

should become 1.

0

No

1

Yes

1

Reserved

0

Reserved

0

GOSTAT

Status of GO operation.

0

GO operation is not in progress.

1

GO operation is in progress.

Phase-Locked Loop Controller (PLLC)

28

SPRUES0B – December 2007