15 clock status register (ckstat), Section 2.4.15 – Texas Instruments TMS320C642x DSP User Manual

Page 32

www.ti.com

2.4.15

Clock Status Register (CKSTAT)

PLL Controller

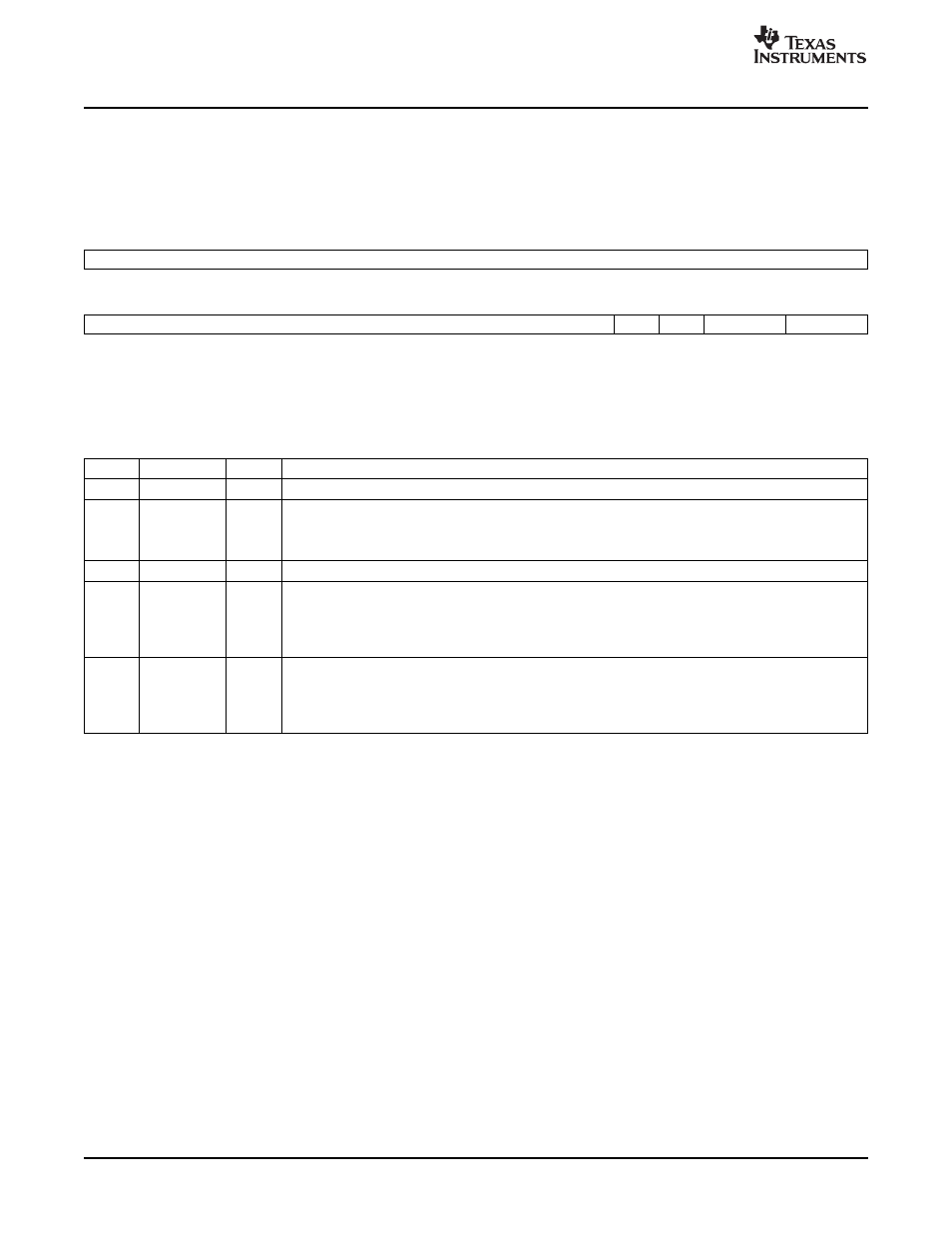

The clock status register (CKSTAT) is shown in

and described in

. CKSTAT shows

clock status for all clocks, except SYSCLKn.

Figure 18. Clock Status Register (CKSTAT)

31

16

Reserved

R-0

15

4

3

2

1

0

Reserved

BPON

Rsvd

OBSON

AUXON

R-0

R-1

R-0

R-0 or 1

(1)

R-0 or 1

(2)

LEGEND: R = Read only; -n = value after reset

(1)

For PLLC1, OBSON defaults to 1; for PLLC2, OBSON is reserved and defaults to 0.

(2)

For PLLC1, AUXON defaults to 1; for PLLC2, AUXON is reserved and defaults to 0.

Table 24. Clock Status Register (CKSTAT) Field Descriptions

Bit

Field

Value

Description

31-4

Reserved

0

Reserved

3

BPON

SYSCLKBP on status. SYSCLKBP is controlled in the bypass divider register (BPDIV).

0

SYSCLKBP is off.

1

SYSCLKBP is on.

2

Reserved

0

Reserved

1

OBSON

OBSCLK on status. OBSCLK is controlled in the oscillator divider 1 register (OSCDIV1) and by the

OBSEN bit in the clock enable control register (CKEN). Not applicable on PLLC2 (this bit is reserved).

0

OBSCLK is off.

1

OBSCLK is on.

0

AUXON

AUXCLK on status. AUXCLK is controlled by the AUXEN bit in the clock enable control register

(CKEN). Not applicable on PLLC2 (this bit is reserved).

0

AUXCLK is off.

1

AUXCLK is on.

32

Phase-Locked Loop Controller (PLLC)

SPRUES0B – December 2007