13 plldiv ratio change status register (dchange), Dchange), Descriptions – Texas Instruments TMS320C642x DSP User Manual

Page 30: Section 2.4.13

www.ti.com

2.4.13

PLLDIV Ratio Change Status Register (DCHANGE)

PLL Controller

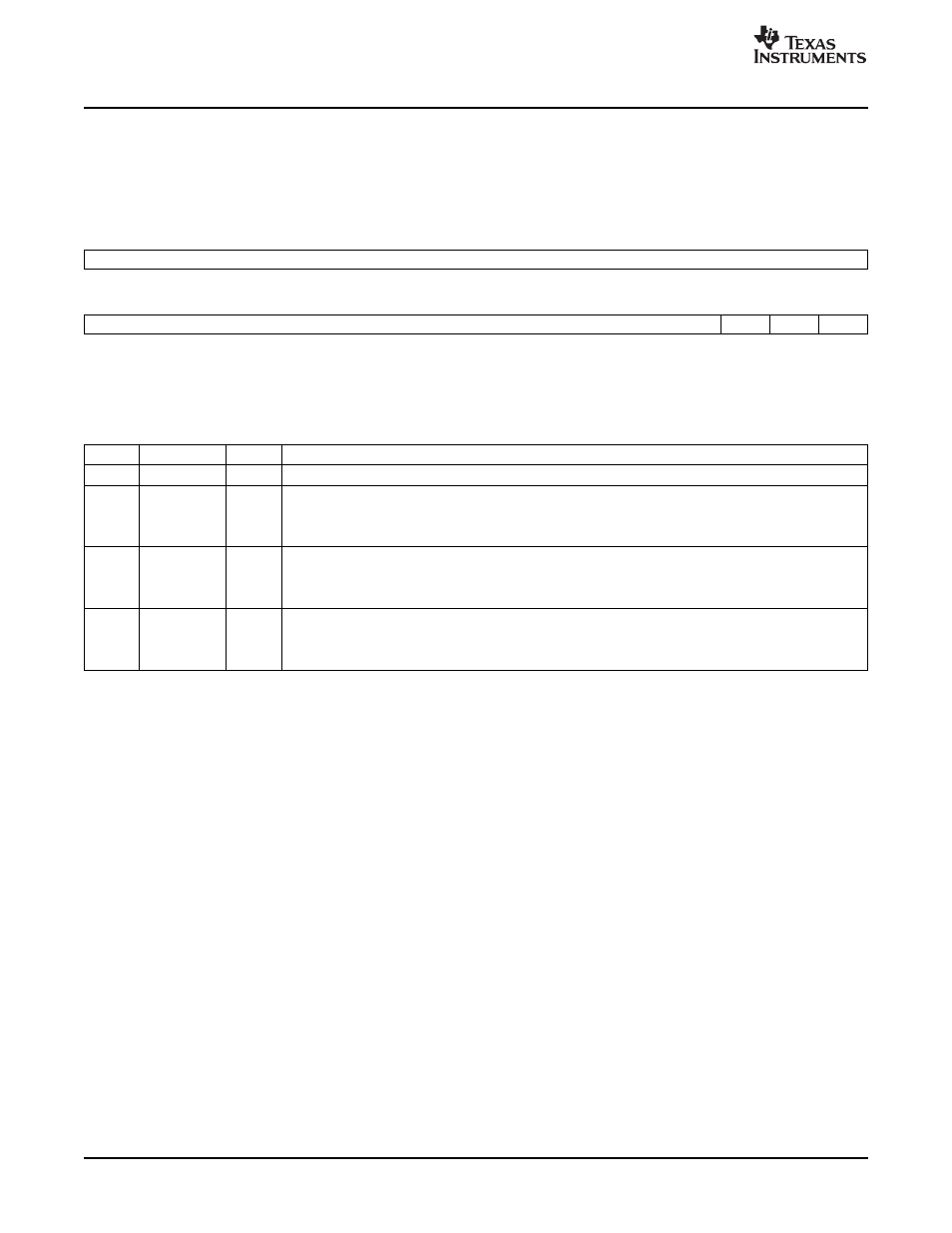

The PLLDIV ratio change status register (DCHANGE) is shown in

and described in

DCHANGE indicates if the SYSCLK divide ratio has been modified.

Figure 16. PLLDIV Ratio Change Status Register (DCHANGE)

31

16

Reserved

R-0

15

3

2

1

0

Reserved

SYS3

SYS2

SYS1

R-0

R-0

(1)

R-0

R-0

LEGEND: R = Read only; -n = value after reset

(1)

For PLLC2, SYS3 is reserved and defaults to 0.

Table 22. PLLDIV Ratio Change Status Register (DCHANGE) Field Descriptions

Bit

Field

Value

Description

31-3

Reserved

0

Reserved

2

SYS3

SYSCLK3 divide ratio is modified. Not applicable on PLLC2 (this bit is reserved).

0

SYSCLK3 divide ratio is not modified.

1

SYSCLK3 divide ratio is modified.

1

SYS2

SYSCLK2 divide ratio is modified.

0

SYSCLK2 divide ratio is not modified.

1

SYSCLK2 divide ratio is modified.

0

SYS1

SYSCLK1 divide ratio is modified.

0

SYSCLK1 divide ratio is not modified.

1

SYSCLK1 divide ratio is modified.

30

Phase-Locked Loop Controller (PLLC)

SPRUES0B – December 2007