Renesas M3028BT-EPB User Manual

Page 63

M3028BT-EPB User’s Manual

3. Usage (Emulator Debugger)

REJ10J1459-0200 Rev.2.00 Sep 16, 2006

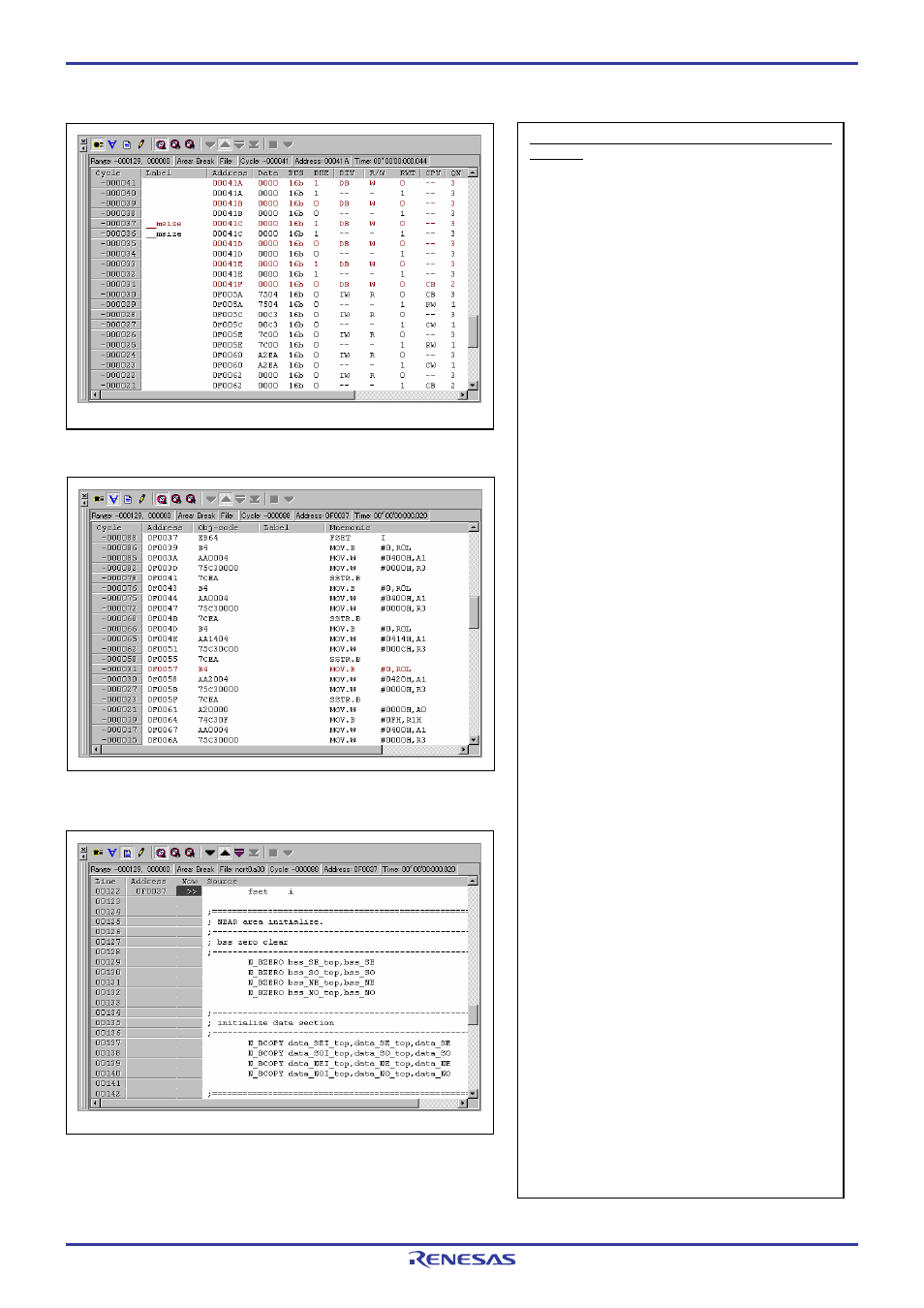

3. Trace window (bus display)

Explanation of the trace window (bus

display)

The following explains the displayed contents, from left to

right.

- Cycle

Shows trace cycles. Double-click here to bring up a

dialog box to change the displayed cycle.

- Label

Shows labels corresponding to address bus information.

Double-click here to bring up a dialog box to search for

addresses.

- Address

Shows the status of the address bus.

- Data

Shows the status of the data bus.

- BUS

Shows the width of the external data bus. In the present

emulator, only “16b” for 16 bits wide bus is displayed.

- BHE

Shows the status (0 or 1) of the BHE (Byte High Enable)

signal. If this signal = 0, the odd-address data is valid.

- BIU

Shows the status between the BIU (Bus Interface Unit)

and memory or I/O.

Symbol Status

– Non-active

DMA

Data access by other than the CPU, e.g., by

DMA

INT

Starts INTACK sequence

IB

Instruction code read by the CPU (in bytes)

DB

Data access by the CPU (in bytes)

IW

Instruction code read by the CPU (in words)

DW

Data access by the CPU (in words)

- R/W

Shows the status of the data bus.

Displayed as “R” for Read, “W” for Write, and “–” for

no access.

- RWT

This is the signal to indicate a valid bus cycle. When

valid, RWT = 0. The Address, Data, and the BIU signals

are effective when this signal is 0.

- CPU

Shows the status between the CPU and BIU (Bus

Interface Unit).

Symbol Status

CB

Op-code read (in bytes)

RB

Operand read (in bytes)

QC

Instruction queue buffer clear

CW

Op-code read (in words)

RW

Operand read (in words)

- QN

Shows the byte count stored in the instruction queue

buffer. The display range is 0 to 4.

- 76543210

Shows the level of external trace signal input cable

EXTIN0 to EXTIN7.

- h” m’ s: ms. us

Shows the elapsed time after starting the user program.

4. Trace window (disassemble display)

5. Trace window (source display)

Page 61 of 86