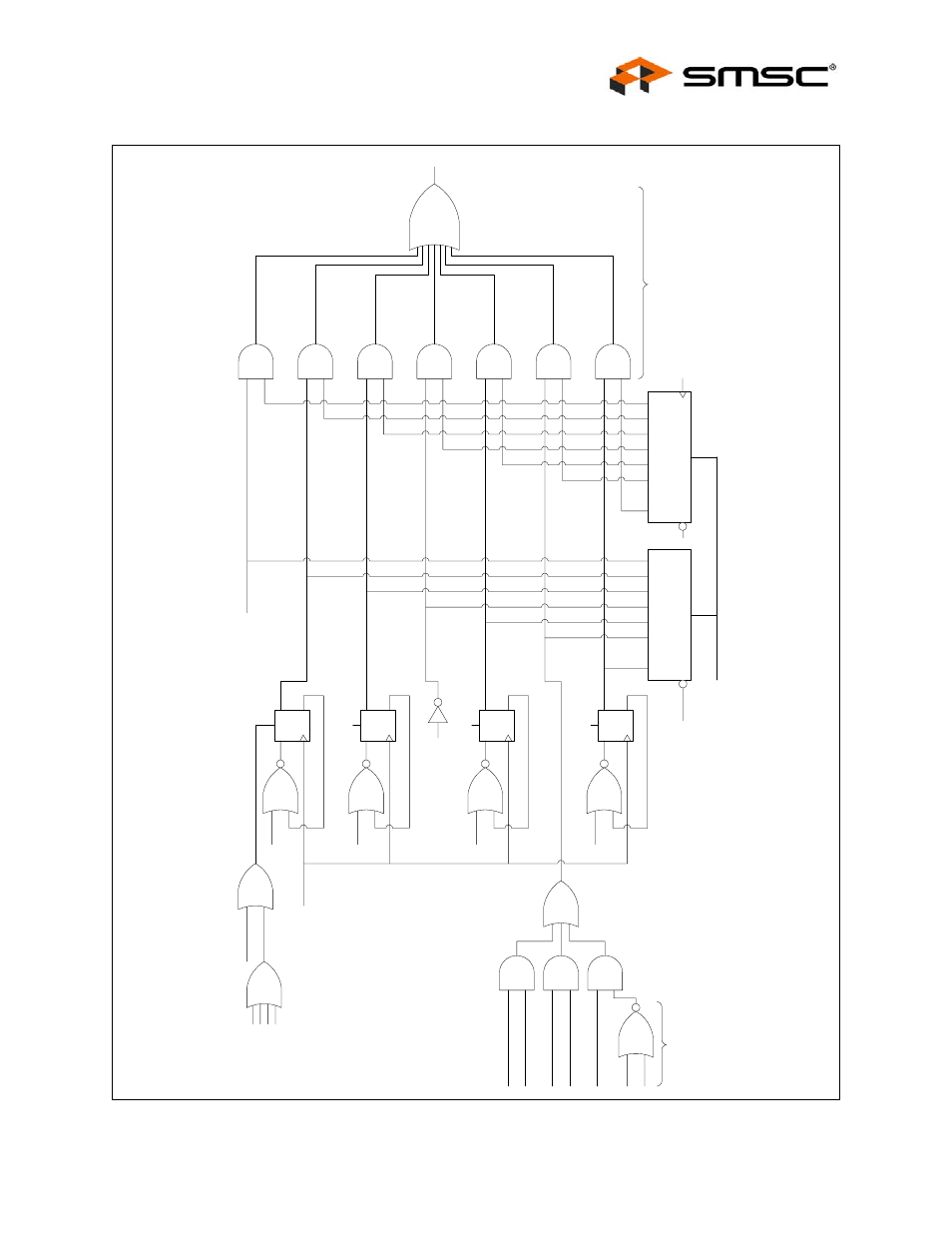

Figure 8.2 interrupt structure, Datasheet – SMSC LAN91C111 User Manual

Page 65

10/100 Non-PCI Ethernet Single Chip MAC + PHY

Datasheet

SMSC LAN91C111 REV C

65

Revision 1.91 (08-18-08)

DATASHEET

Figure 8.2 Interrupt Structure

T

X

FI

FO

E

M

PT

Y

DQ

S

nQ

Int

A

ck

1

DQ

S

nQ

Int

A

ck

2

DQ

S

nQ

Int

A

ck

4

DQ

S

nQ

Int

A

ck

7

RX_

O

VRN

MD

IN

T

n

W

RACK

TX Com

p

le

te

Fa

tal

TX

E

rr

o

r

SQ

E

T

L

O

S

T

CARR

LAT

C

O

L

16

C

O

L

Inte

rr

u

p

t St

at

us

R

egi

s

ter

7

6

5432

10

n

RDIS

T

Inter

rupt

Mask

Reg

ister

7

6

5432

1

0

OE

nOE

E

d

ge

D

e

te

ct

o

r on

Li

n

k

Er

r

LEM

A

S

K

CT

R

-RO

L

CR

M

A

SK

TE

M

A

SK

TX

E

N

A

TX

_

S

VC

E

P

HSR I

N

TERRUP

T

S

ME

R

G

ED INTO

E

P

H INT

AL

LO

CA

TI

ON

FA

IL

ED

RX_

O

VRN INT

EP

H INT

MD

IN

T

AL

LO

C

I

N

T

T

X

E

M

P

T

Y

IN

T

T

X

INT

RC

V

I

N

T

INT

RC

V

FIF

O

NOT E

M

PTY

D

[7:

0]

D[1

5

:8

]

DATA

B

U

S

D[1

5

:0

]

M

A

IN INTERRU

P

T

S