Datasheet – SMSC LAN91C111 User Manual

Page 101

10/100 Non-PCI Ethernet Single Chip MAC + PHY

Datasheet

SMSC LAN91C111 REV C

101

Revision 1.91 (08-18-08)

DATASHEET

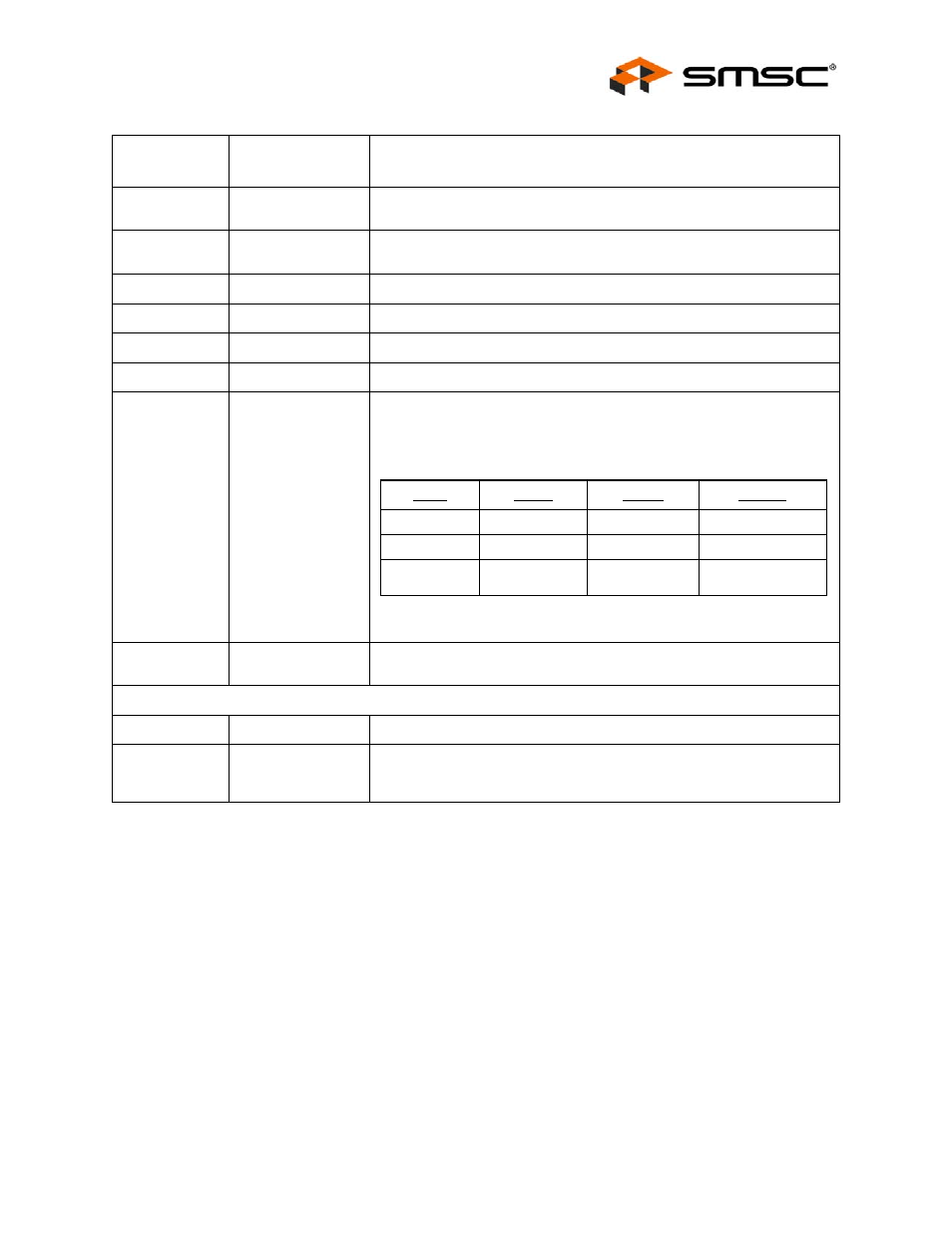

nIOWR

nWR

I/O Write strobe - asynchronous write access. Address is valid before

leading edge. Data is latched on trailing edge.

IOCHRDY

ARDY

This signal is negated on leading nRD, nWR if necessary. It is then

asserted on CLK rising edge after the access condition is satisfied.

RESET

RESET

A0

nBE0

nSBHE

nBE1

IRQn

INTR0

D0-D15

D0-D15

16 bit data bus. The bus byte(s) used to access the device are a function

of nBE0 and nBE1:

Not used = tri-state on reads, ignored on writes

nIOCS16

nLDEV buffered

nLDEV is a totem pole output. Must be buffered using an open collector

driver. nLDEV is active on valid decodes of A15-A4 and AEN=0.

UNUSED PINS

GND

nADS

VCC

nBE2, nBE3,

nCYCLE, W/nR,

nRDYRTN, LCLK

No upper word access.

Table 12.2 High-End ISA or Non-Burst EISA Machines Signal Connectors (continued)

ISA BUS

SIGNAL

LAN91C111

SIGNAL

NOTES

nBE0

nBE1

D0-D7

D8-D15

0

0

Lower

Upper

0

1

Lower

Not used

1

0

Not used

Upper