Figure 12.2 lan91c111 on isa bus, Table 12.3 eisa 32 bit slave signal connections, Isa bus – SMSC LAN91C111 User Manual

Page 102: Datasheet

10/100 Non-PCI Ethernet Single Chip MAC + PHY

Datasheet

Revision 1.91 (08-18-08)

102

SMSC LAN91C111 REV C

DATASHEET

EISA 32 BIT SLAVE

On EISA the LAN91C111 is accessed as a 32 bit I/O slave, along with a Slave DMA type "C" data

path option. As an I/O slave, the LAN91C111 uses asynchronous accesses. In creating nRD and nWR

inputs, the timing information is externally derived from nCMD edges. Given that the access will be at

least 1.5 to 2 clocks (more than 180ns at least) there is no need to negate EXRDY, simplifying the

EISA interface implementation. As a DMA Slave, the LAN91C111 accepts burst transfers and is able

to sustain the peak rate of one doubleword every BCLK. Doubleword alignment is assumed for DMA

transfers. The LAN91C111 will sample EXRDY and postpone DMA cycles if the memory cycle solicits

wait states.

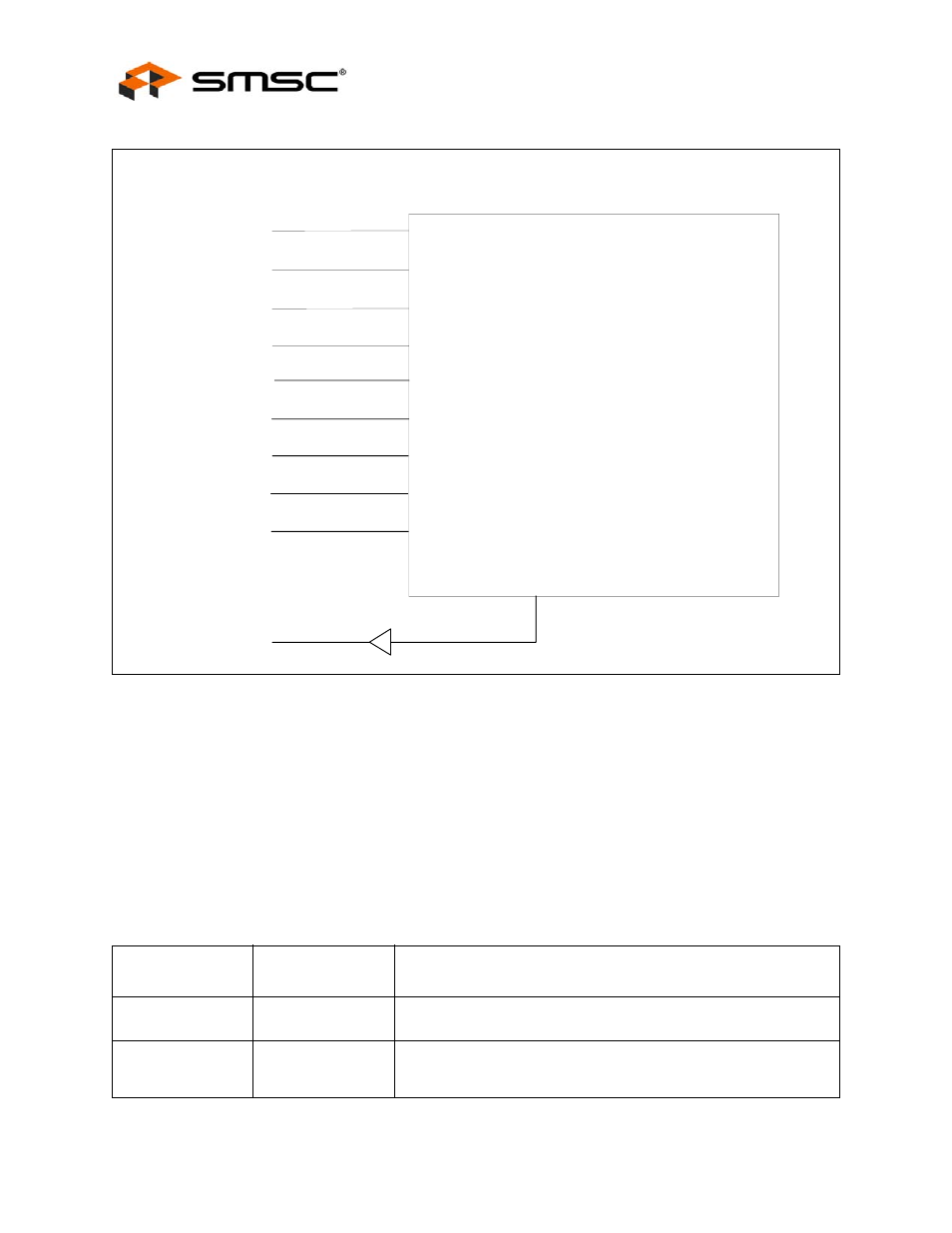

Figure 12.2 LAN91C111 on ISA BUS

Table 12.3 EISA 32 Bit Slave Signal Connections

EISA BUS

SIGNAL

LAN91C111

SIGNAL

NOTES

LA2-LA15

A2-A15

Address bus used for I/O space and register decoding, latched by

nADS (nSTART) trailing edge.

M/nIO

AEN

AEN

Qualifies valid I/O decoding - enabled access when low. These

signals are externally ORed. Internally the AEN pin is latched by

nADS rising edge and transparent while nADS is low.

A1-A15, AEN

RESET

nBE2, nBE3

D0-D15

INTR0

nRD

nWR

nBE0

nBE1

nLDEV

LAN91C111

A1-A15, AEN

RESET

VCC

D0-D15

IRQ

nIORD

nIOWR

A0

nSBHE

nIOCS16

O.C.

ISA BUS