16 bank 2 - mmu command register, Bank 2 - mmu command register, Datasheet – SMSC LAN91C111 User Manual

Page 58

10/100 Non-PCI Ethernet Single Chip MAC + PHY

Datasheet

Revision 1.91 (08-18-08)

58

SMSC LAN91C111 REV C

DATASHEET

8.16

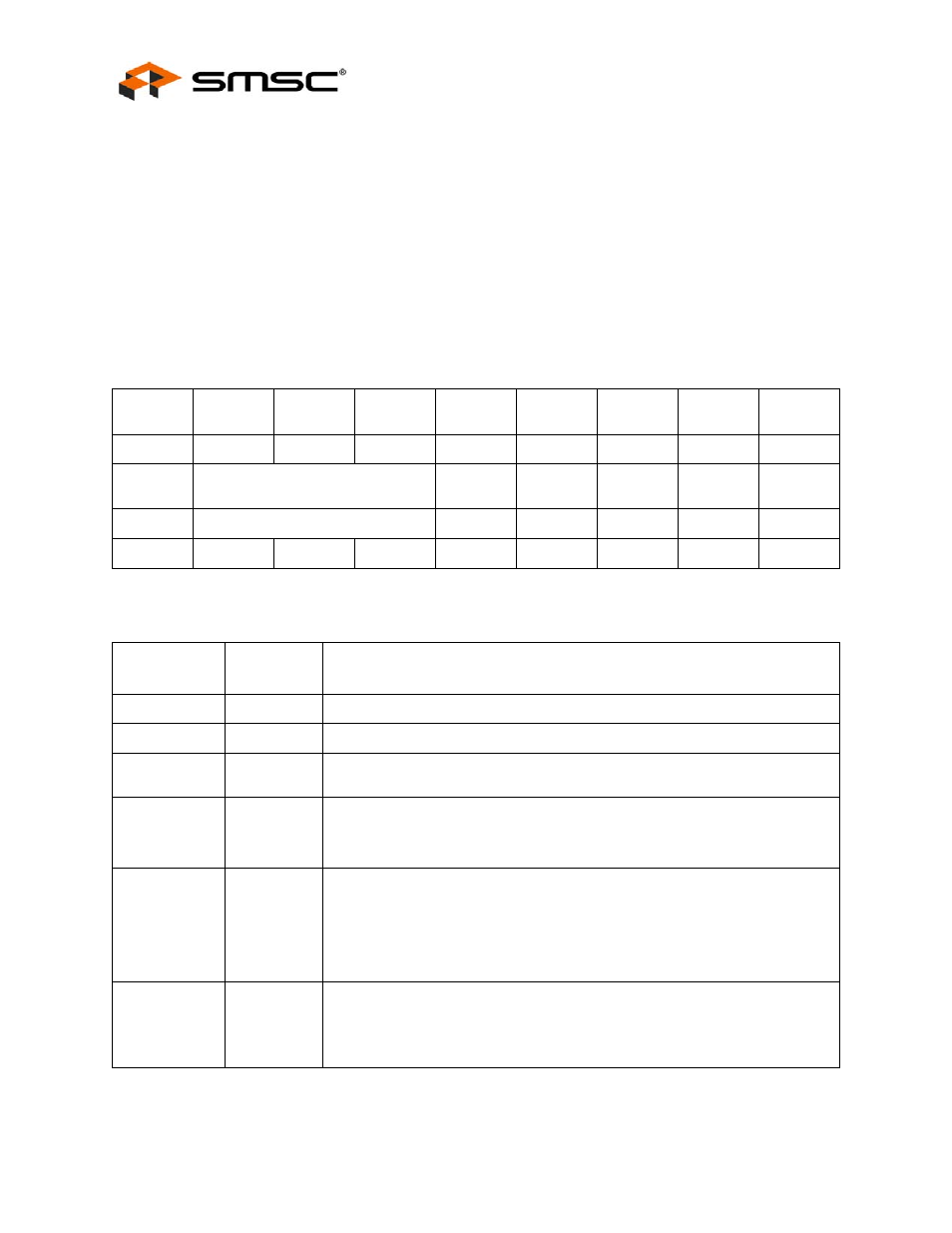

Bank 2 - MMU Command Register

This register is used by the CPU to control the memory allocation, de-allocation, TX FIFO and RX

FIFO control.

The three command bits determine the command issued as described below:

COMMAND SET:

OFFSET

NAME

TYPE

SYMBOL

0

MMU COMMAND

REGISTER

WRITE ONLY

BUSY BIT

READABLE

MMUCR

HIGH

BYTE

LOW

BYTE

COMMAND

Reserved

Reserved

Reserved

Reserved

BUSY

Operation Code

0

OPERATION

CODE

DECIMAL

VALUE

COMMAND

000

0

NOOP - NO OPERATION

001

1

ALLOCATE MEMORY FOR TX

010

2

RESET MMU TO INITIAL STATE - Frees all memory allocations, clears relevant

interrupts, resets packet FIFO pointers.

011

3

REMOVE FRAME FROM TOP OF RX FIFO - To be issued after CPU has

completed processing of present receive frame. This command removes the

receive packet number from the RX FIFO and brings the next receive frame (if

any) to the RX area (output of RX FIFO).

100

4

REMOVE AND RELEASE TOP OF RX FIFO - Like 3) but also releases all

memory used by the packet presently at the RX FIFO output. The MMU busy

time after issuing REMOVE and RELEASE command depends on the time when

the busy bit is cleared. The time from issuing REMOVE and RELEASE command

on the last receive packet to the time when receive FIFO is empty depends on

RX INT bit turning low. An alternate approach can be checking the read RX FIFO

register.

101

5

RELEASE SPECIFIC PACKET - Frees all pages allocated to the packet specified

in the PACKET NUMBER REGISTER. Should not be used for frames pending

transmission. Typically used to remove transmitted frames, after reading their

completion status. Can be used following 3) to release receive packet memory

in a more flexible way than 4).