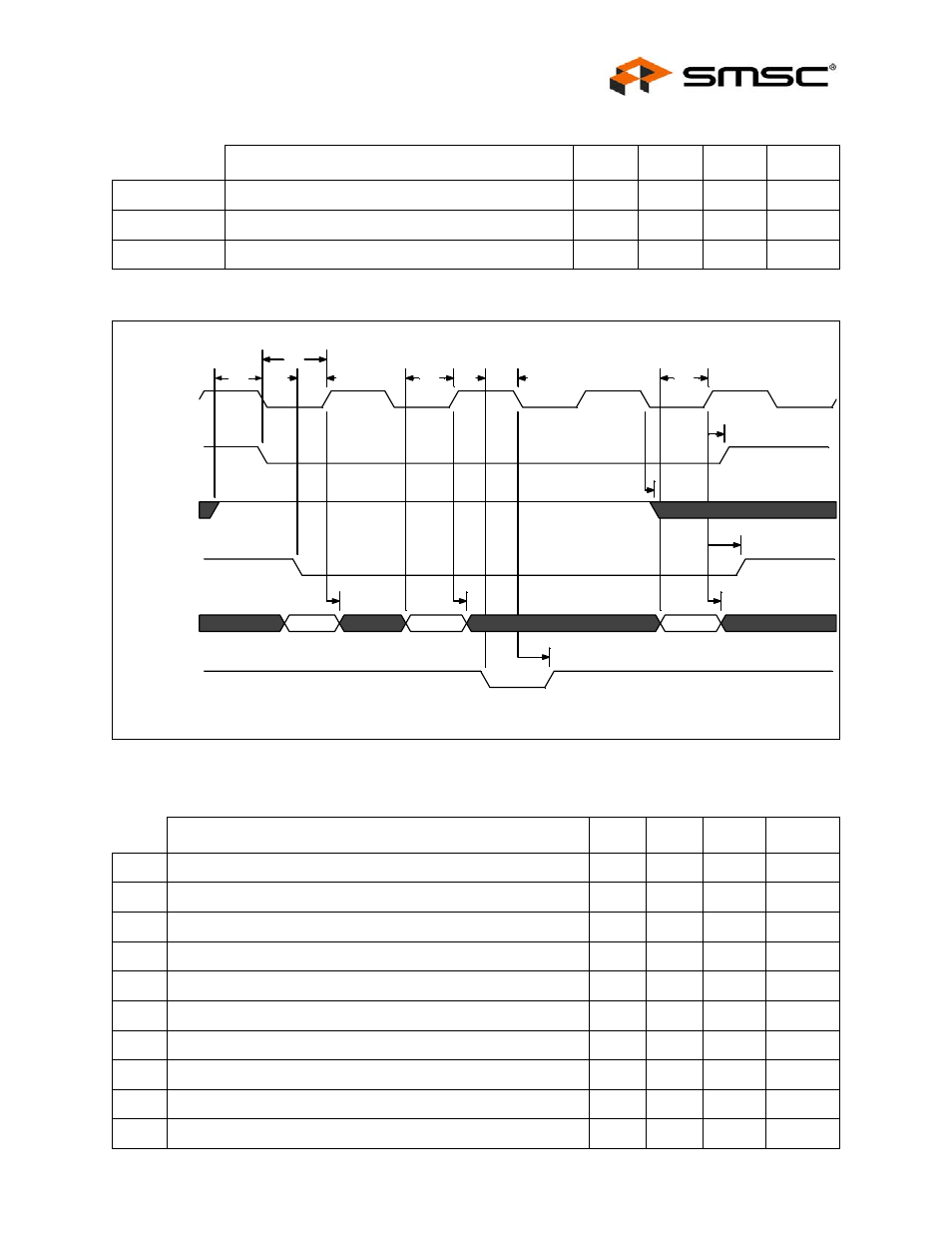

Figure 14.5 burst write cycles - nvlbus=1, Datasheet – SMSC LAN91C111 User Manual

Page 113

10/100 Non-PCI Ethernet Single Chip MAC + PHY

Datasheet

SMSC LAN91C111 REV C

113

Revision 1.91 (08-18-08)

DATASHEET

PARAMETER

MIN

TYP

MAX

UNITS

t26

ARDY Low Pulse Width

100

150

ns

t26A

Control Active to ARDY Low

10

ns

t13

Valid Data to ARDY High

10

ns

Figure 14.5 Burst Write Cycles - nVLBUS=1

PARAMETER

MIN

TYP

MAX

UNITS

t12

nDATACS Setup to LCLK Rising

20

ns

t12A

nDATACS Hold After LCLK Rising

0

ns

t14

nRDYRTN Setup to LCLK Falling

10

ns

t15

nRDYRTN Hold after LCLK Falling

10

ns

t17

W/nR Setup to LCLK Falling

15

ns

t17A

W/nR Hold After LCLK Falling

3

ns

t18

Data Setup to LCLK Rising (Write)

15

ns

t20

Data Hold from LCLK Rising (Write)

4

ns

t22

nCYCLE Setup to LCLK Rising

5

ns

t22A

nCYCLE Hold After LCLK Rising

10

ns

t15

t20

t20

t20

t22A

t17A

t12A

t18

t14

t18

t12

t22

t17

a

b

c

Clock

nDATACS

W/nR

nCYCLE

Write Data

nRDYRTN