9 bank 0 - memory information register, 10 bank 0 - receive/phy control register, Bank 0 - memory information register – SMSC LAN91C111 User Manual

Page 51: Bank 0 - receive/phy control register, Datasheet

10/100 Non-PCI Ethernet Single Chip MAC + PHY

Datasheet

SMSC LAN91C111 REV C

51

Revision 1.91 (08-18-08)

DATASHEET

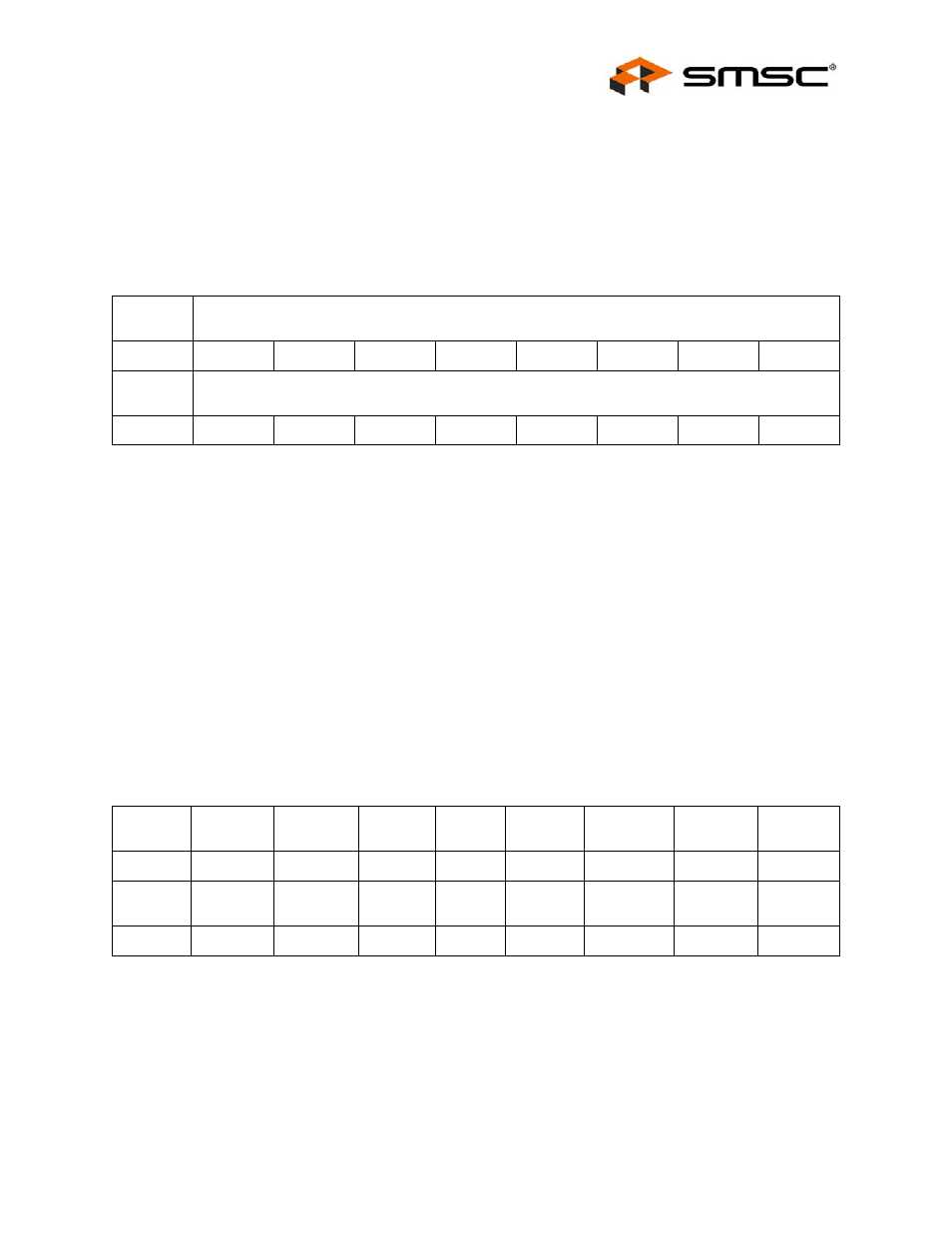

8.9

Bank 0 - Memory Information Register

FREE MEMORY AVAILABLE - This register can be read at any time to determine the amount of free

memory. The register defaults to the MEMORY SIZE upon POR (Power On Reset) or upon the RESET

MMU command.

MEMORY SIZE - This register can be read to determine the total memory size.

All memory related information is represented in 2K * M byte units, where the multiplier M is 1 for

LAN91C111.

8.10

Bank 0 - Receive/Phy Control Register

SPEED – Speed select Input. This bit is valid and selects 10/100 PHY operation only when the ANEG

Bit = 0, this bit overrides the SPEED bit in the PHY Register 0 (Control Register) and determine the

speed mode. When this bit is set (1), the Internal PHY will operate at 100Mbps. When this bit is

cleared (0), the Internal PHY will operate at 10Mbps. When the ANEG bit = 1, this bit is ignored and

10/100 operation is determined by the outcome of the Auto-negotiation or this bit is overridden by the

SPEED bit in the PHY Register 0 (Control Register) when the ANEG_EN bit in the PHY Register 0

(Control Register) is clear.

DPLX – Duplex Select - This bit selects Full/Half Duplex operation. This bit is valid and selects duplex

operation only when the ANEG Bit = 0, this bit overrides the DPLX bit in the PHY Register 0 (Control

OFFSET

NAME

TYPE

SYMBOL

8

MEMORY INFORMATION

REGISTER

READ ONLY

MIR

HIGH

BYTE

FREE MEMORY AVAILABLE (IN BYTES * 2K * M)

0

0

0

0

0

1

0

0

LOW

BYTE

MEMORY SIZE (IN BYTES *2K * M)

0

0

0

0

0

1

0

0

OFFSET

NAME

TYPE

SYMBOL

A

RECEIVE/PHY CONTROL

REGISTER

READ/WRITE

RPCR

HIGH

BYTE

Reserved

Reserved

SPEED

DPLX

ANEG

Reserved

Reserved

Reserved

0

0

0

0

0

0

0

0

LOW

BYTE

LS2A

LS1A

LS0A

LS2B

LS1B

LS0B

Reserved

Reserved

0

0

0

0

0

0

0

0