Figure 14.3 asynchronous cycle - nads=0, Figure 14.4 asynchronous ready, Datasheet – SMSC LAN91C111 User Manual

Page 112

10/100 Non-PCI Ethernet Single Chip MAC + PHY

Datasheet

Revision 1.91 (08-18-08)

112

SMSC LAN91C111 REV C

DATASHEET

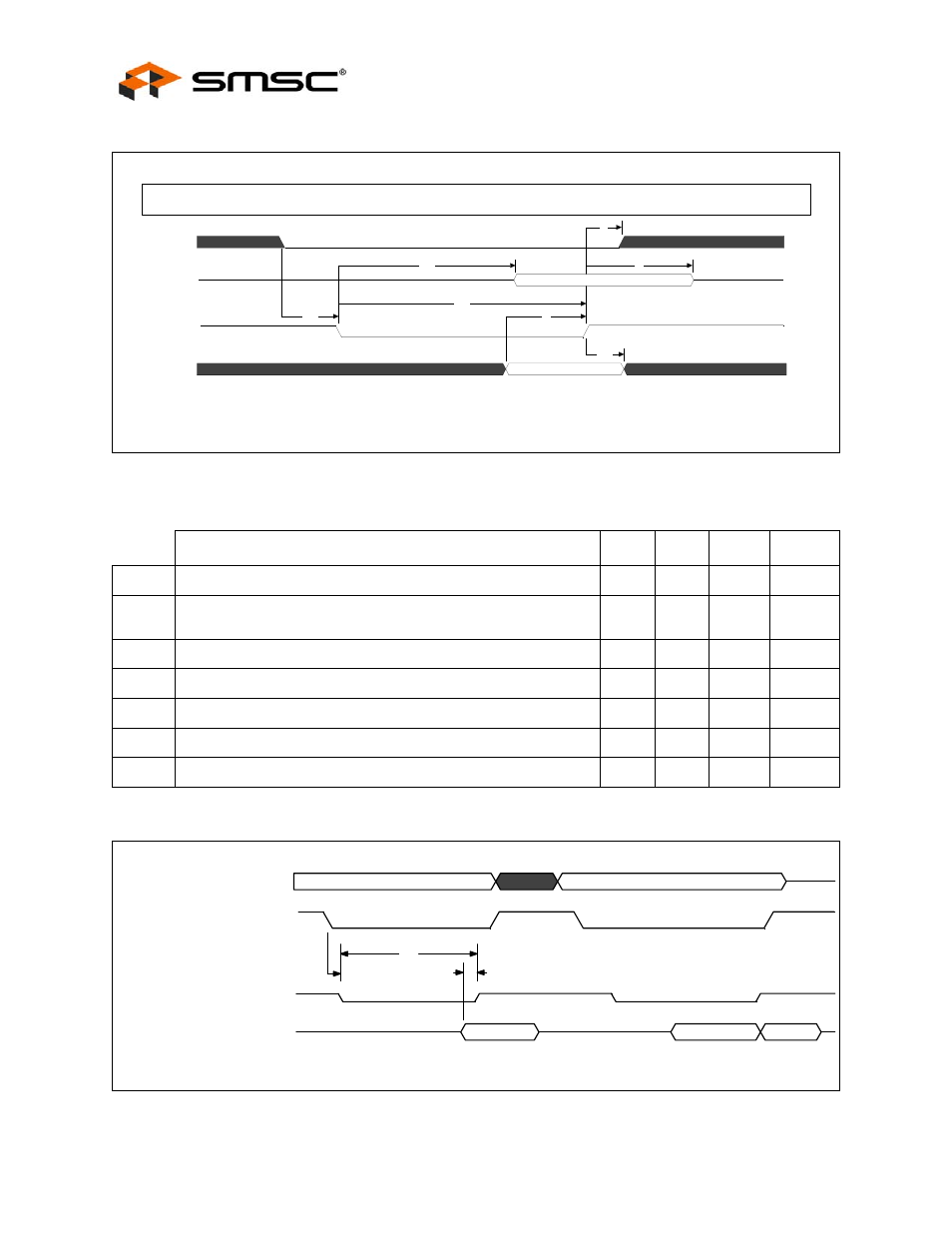

Figure 14.3 Asynchronous Cycle - nADS=0

PARAMETER

MIN

TYP

MAX

UNITS

t1A

nDATACS Setup to nRD, nWR Active

2

ns

t2

nDATACS Hold After nRD, nWR Inactive (Assuming nADS Tied

Low)

5

ns

t3A

nRD Low to Valid Data

30

ns

t4

nRD High to Data Invalid

2

15

ns

t5

Data Setup to nWR Inactive

10

ns

t5A

Data Hold After nWR Inactive

5

ns

t6A

nRD Strobe Width

30

ns

Figure 14.4 Asynchronous Ready

t5A

t5

t6A

t1A

t4

t3A

t2

valid

D0~D31 valid

0ns

50ns

100ns

150ns

200ns

250n

nDATACS

Read Data

nRD,nWR

Write Data

Asynchronous Cycle - nADS=0

t26A

t13

t26

t26

Valid Data

Valid Address

Valid Address

Valid

Address, AEN, nBE[3:0]

nRD, nWR

ARDY

Data