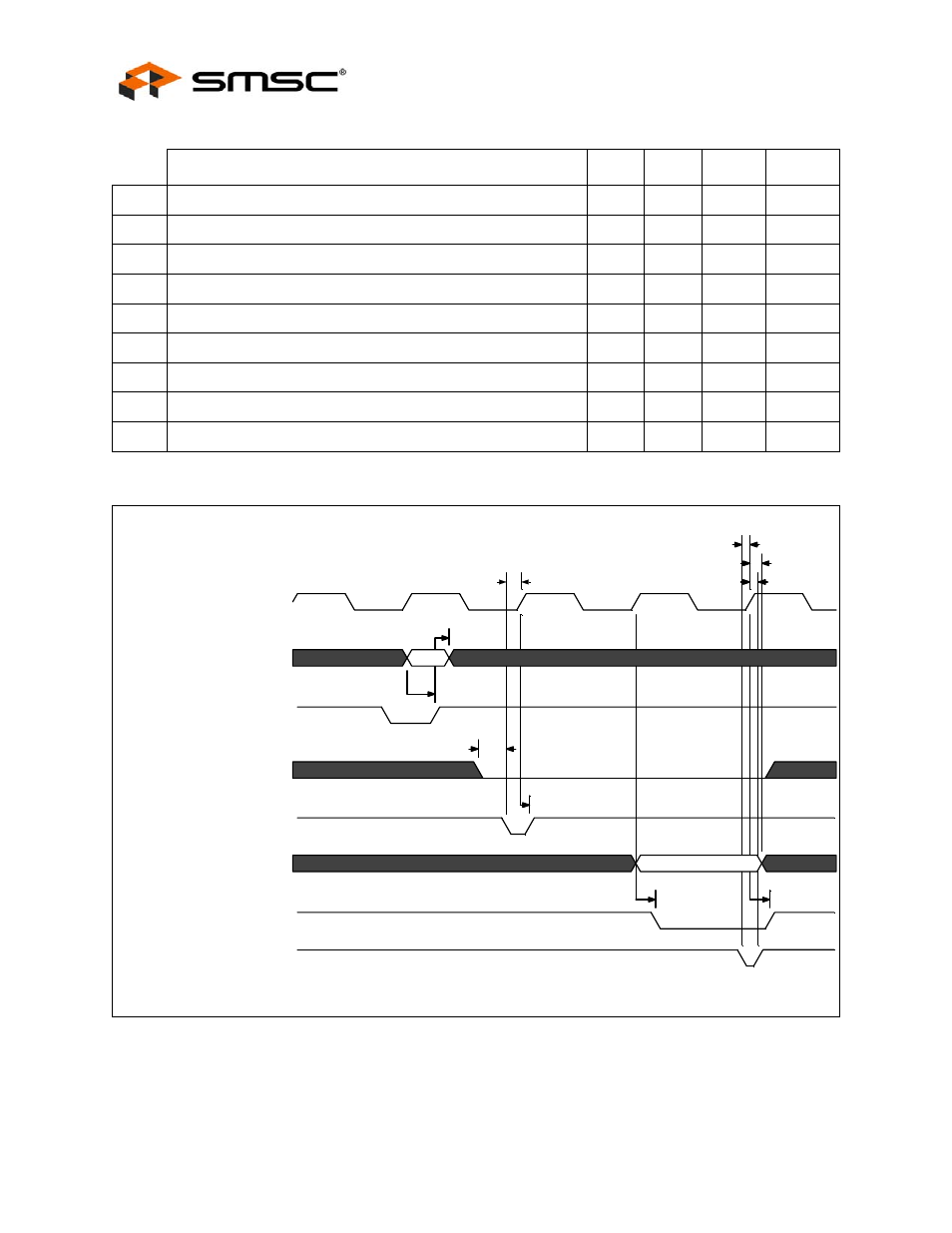

Figure 14.9 synchronous read cycle - nvlbus=0, Datasheet – SMSC LAN91C111 User Manual

Page 116

10/100 Non-PCI Ethernet Single Chip MAC + PHY

Datasheet

Revision 1.91 (08-18-08)

116

SMSC LAN91C111 REV C

DATASHEET

PARAMETER

MIN

TYP

MAX

UNITS

t8

A1-A15, AEN, nBE[3:0] Setup to nADS Rising

8

ns

t9

A1-A15, AEN, nBE[3:0] Hold After nADS Rising

5

ns

t10

nCYCLE Setup to LCLK Rising

5

ns

t11

nCYCLE Hold after LCLK Rising (Non-Burst Mode)

3

ns

t16

W/nR Setup to nCYCLE Active

0

ns

t17A

W/nR Hold after LCLK Rising with nSRDY Active

3

ns

t18

Data Setup to LCLK Rising (Write)

15

ns

t20

Data Hold from LCLK Rising (Write)

4

ns

t21

nSRDY Delay from LCLK Rising

7

ns

Figure 14.9 Synchronous Read Cycle - nVLBUS=0

t21

t21

t11

t8

t9

t16

t23

t24

t20

t10

Valid

Valid

Clock

Address, AEN, nBE[3:0]

nADS

W/nR

nCYCLE

Read Data

nSRDY

nRDYRTN