7 bank 0 - receive control register, Bank 0 - receive control register, Datasheet – SMSC LAN91C111 User Manual

Page 49

10/100 Non-PCI Ethernet Single Chip MAC + PHY

Datasheet

SMSC LAN91C111 REV C

49

Revision 1.91 (08-18-08)

DATASHEET

SQET - Signal Quality Error Test. This bit is set under the following conditions:

1. LAN91C111 is set to operate in Half Duplex mode (SWFDUP=0);

2. When STP_SQET=1 and SWFDUP=0, SQET bit will be set upon completion of a transmit

operation and no SQET Pulse has occurred during the IPG (Inter Frame Gap). If a pulse has

occurred during the IPG, SQET bit will not get set.

3. Once SQET bit is set, setting the TXENA bit in TCR register, or via hardware /software reset can

clear this bit.

16COL - 16 collisions reached. Set when 16 collisions are detected for a transmit frame. TXENA bit

in TCR is reset. Cleared when TXENA is set high.

LTX_MULT - Last transmit frame was a multicast. Set if frame was a multicast. Cleared at the start

of every transmit frame.

MULCOL - Multiple collision detected for the last transmit frame. Set when more than one collision

was experienced. Cleared when TX_SUC is high at the end of the packet being sent.

SNGLCOL - Single collision detected for the last transmit frame. Set when a collision is detected.

Cleared when TX_SUC is high at the end of the packet being sent.

TX_SUC - Last transmit was successful. Set if transmit completes without a fatal error. This bit is

cleared by the start of a new frame transmission or when TXENA is set high. Fatal errors are:

16 collisions (1/2 duplex mode only)

SQET fail and STP_SQET = 1 (1/2 duplex mode only)

Carrier lost and MON_CSN = 1 (1/2 duplex mode only)

Late collision (1/2 duplex mode only)

8.7

Bank 0 - Receive Control Register

SOFT_RST - Software-Activated Reset. Active high. Initiated by writing this bit high and terminated by

writing the bit low. The LAN91C111’s configuration is not preserved except for Configuration, Base,

and IA0-IA5 Registers. EEPROM is not reloaded after software reset.

FILT_CAR - Filter Carrier. When set filters leading edge of carrier sense for 12 bit times (3 nibble

times). Otherwise recognizes a receive frame as soon as carrier sense is active. (Does NOT filter RX

DV on MII!)

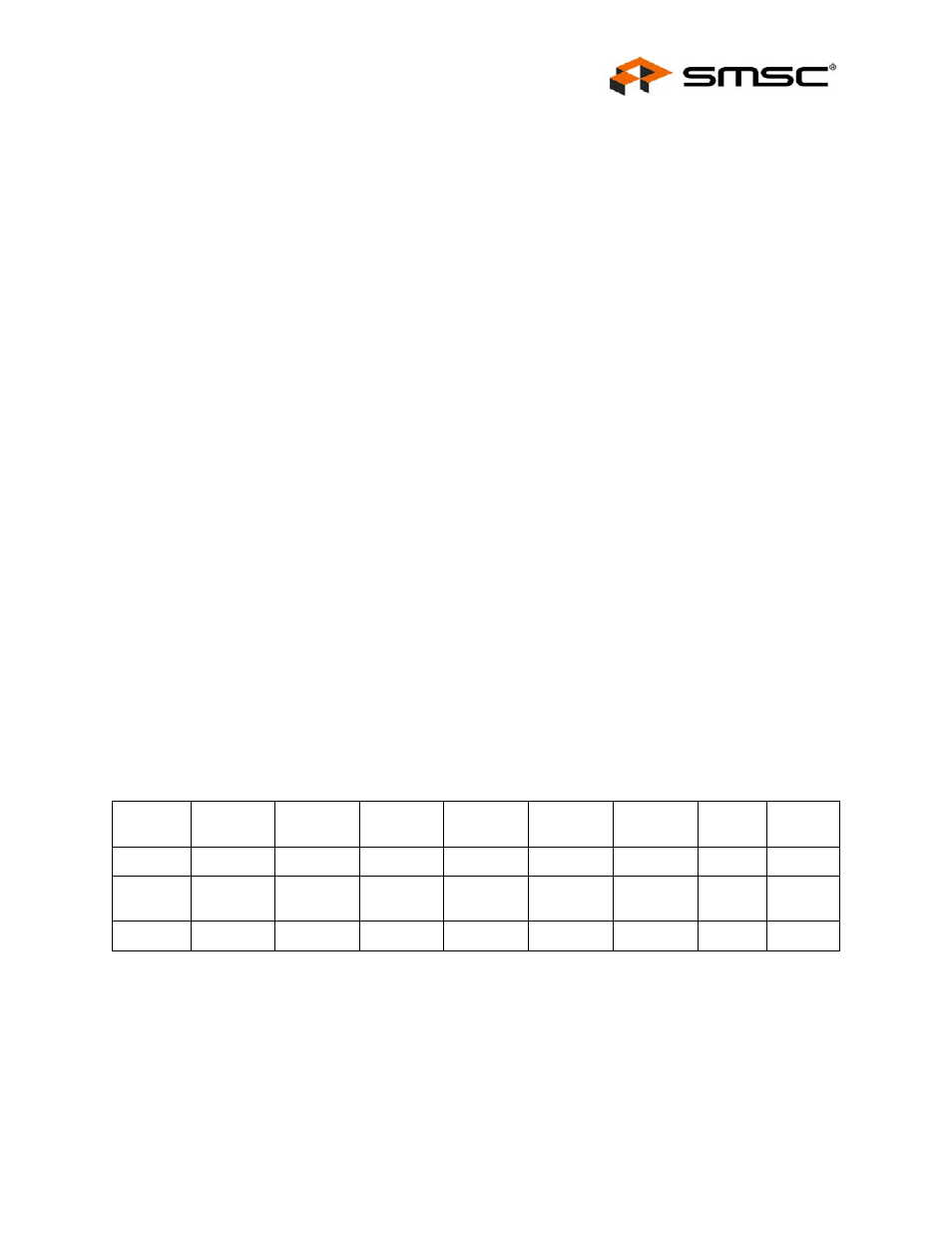

OFFSET

NAME

TYPE

SYMBOL

4

RECEIVE CONTROL

REGISTER

READ/WRITE

RCR

HIGH

BYTE

SOFT

RST

FILT

CAR

ABORT_E

NB

Reserved

Reserved

Reserved

STRIP

CRC

RXEN

0

0

0

0

0

0

0

0

LOW

BYTE

Reserved

Reserved

Reserved

Reserved

Reserved

ALMUL

PRMS

RX_

ABORT

0

0

0

0

0

0

0

0