18 bank 2 - fifo ports register, Bank 2 - fifo ports register, Datasheet – SMSC LAN91C111 User Manual

Page 60

10/100 Non-PCI Ethernet Single Chip MAC + PHY

Datasheet

Revision 1.91 (08-18-08)

60

SMSC LAN91C111 REV C

DATASHEET

This register is updated upon an ALLOCATE MEMORY MMU command.

FAILED - A zero indicates a successful allocation completion. If the allocation fails the bit is set and

only cleared when the pending allocation is satisfied. Defaults high upon reset and reset MMU

command. For polling purposes, the ALLOC_INT in the Interrupt Status Register should be used

because it is synchronized to the read operation. Sequence:

1. Allocate Command

2. Poll ALLOC_INT bit until set

3. Read Allocation Result Register

ALLOCATED PACKET NUMBER - Packet number associated with the last memory allocation request.

The value is only valid if the FAILED bit is clear.

Note: For software compatibility with future versions, the value read from the ARR after an allocation

request is intended to be written into the PNR as is, without masking higher bits (provided

FAILED = 0).

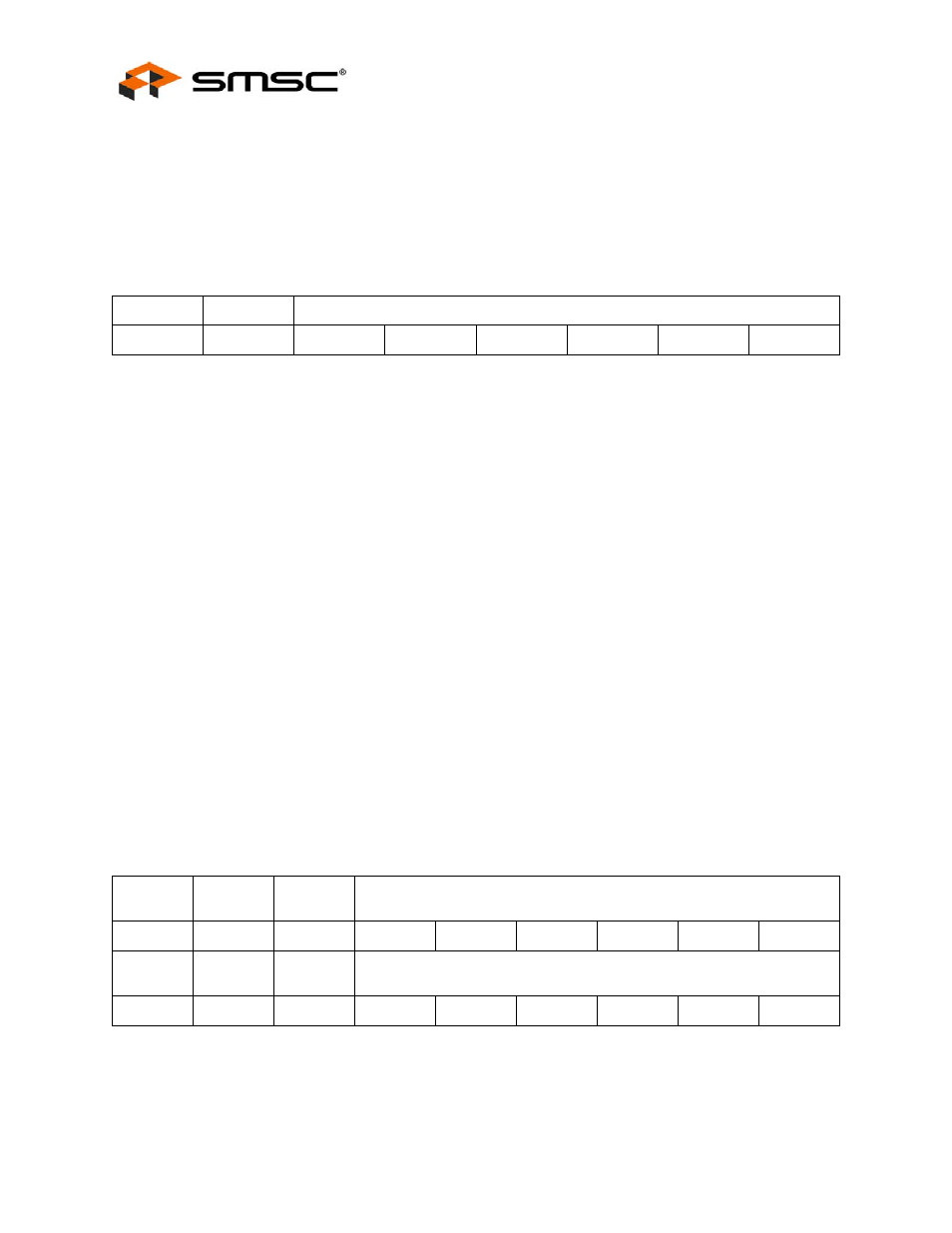

8.18

Bank 2 - FIFO Ports Register

This register provides access to the read ports of the Receive FIFO and the Transmit completion FIFO.

The packet numbers to be processed by the interrupt service routines are read from this register.

REMPTY - No receive packets queued in the RX FIFO. For polling purposes, uses the RCV_INT bit

in the Interrupt Status Register.

TOP OF RX FIFO PACKET NUMBER - Packet number presently at the output of the RX FIFO. Only

valid if REMPTY is clear. The packet is removed from the RX FIFO using MMU Commands 3) or 4).

OFFSET

NAME

TYPE

SYMBOL

3

ALLOCATION RESULT

REGISTER

READ ONLY

ARR

FAILED

Reserved

ALLOCATED PACKET NUMBER

1

0

0

0

0

0

0

0

OFFSET

NAME

TYPE

SYMBOL

4

FIFO PORTS REGISTER

READ ONLY

FIFO

HIGH

BYTE

REMPTY

Reserved

RX FIFO PACKET NUMBER

1

0

0

0

0

0

0

0

LOW

BYTE

TEMPTY

Reserved

TX FIFO PACKET NUMBER

1

0

0

0

0

0

0

0