Figure 3.2 block diagram, Datasheet – SMSC LAN91C111 User Manual

Page 12

10/100 Non-PCI Ethernet Single Chip MAC + PHY

Datasheet

Revision 1.91 (08-18-08)

12

SMSC LAN91C111 REV C

DATASHEET

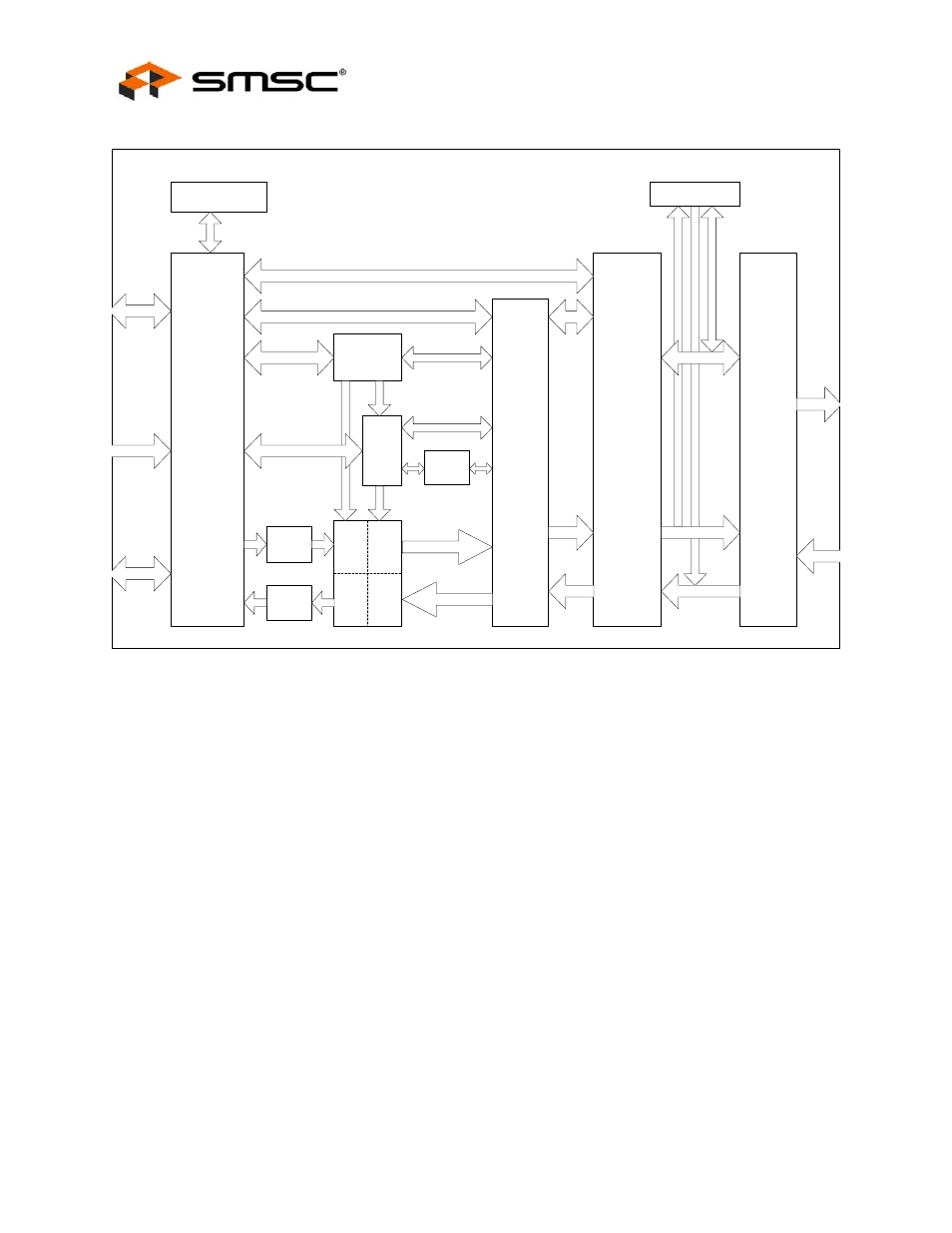

describes the supported Host interfaces, which include ISA or

Generic Embedded. The Host interface is an 8, 16 or 32 bit wide address / data bus with extensions

for 32, 16 and 8 bit embedded RISC and ARM processors.

The figure shown next page describes the SMSC LAN91C111 functional blocks required to integrate

a 10/100 Ethernet Physical layer framer to the internal MAC.

Figure 3.2 Block Diagram

8-32 bit

Bus

Interface

Unit

Arbiter

DMA

MMU

Ethernet

Protocol

Handler

(EPH)

10/100

PHY

8K Byte

Dynamically

Allocated

SRAM

WR

FIFO

RD

FIFO

Control

RX Data

TX Data

Control

Control

MII

Address

Data

Control

Control

RXD[0-3]

TXD[0-3]

Control

TX/RX

FIFO

Pointer

TPI

TPO

Control

EEPROM

INTERFACE

32-bit Data

32-bit Data