2 integration inputs register at 0x1e04, Table 4-2, Smc_int_cfg register bit assignments -3 – SMC Networks ARM PL241 User Manual

Page 87: Table 4-3, Smc_int_inputs register bit assignments -3, Figure 4-3

Programmer’s Model for Test

ARM DDI 0389B

Copyright © 2006 ARM Limited. All rights reserved.

4-3

Table 4-2 lists the register bit assignments.

4.1.2

Integration Inputs Register at 0x1E04

The read-only smc_int_inputs Register enables an external master to access the inputs

of the SMC using the APB interface. This register is only for test. This register cannot

be read in the Reset state.

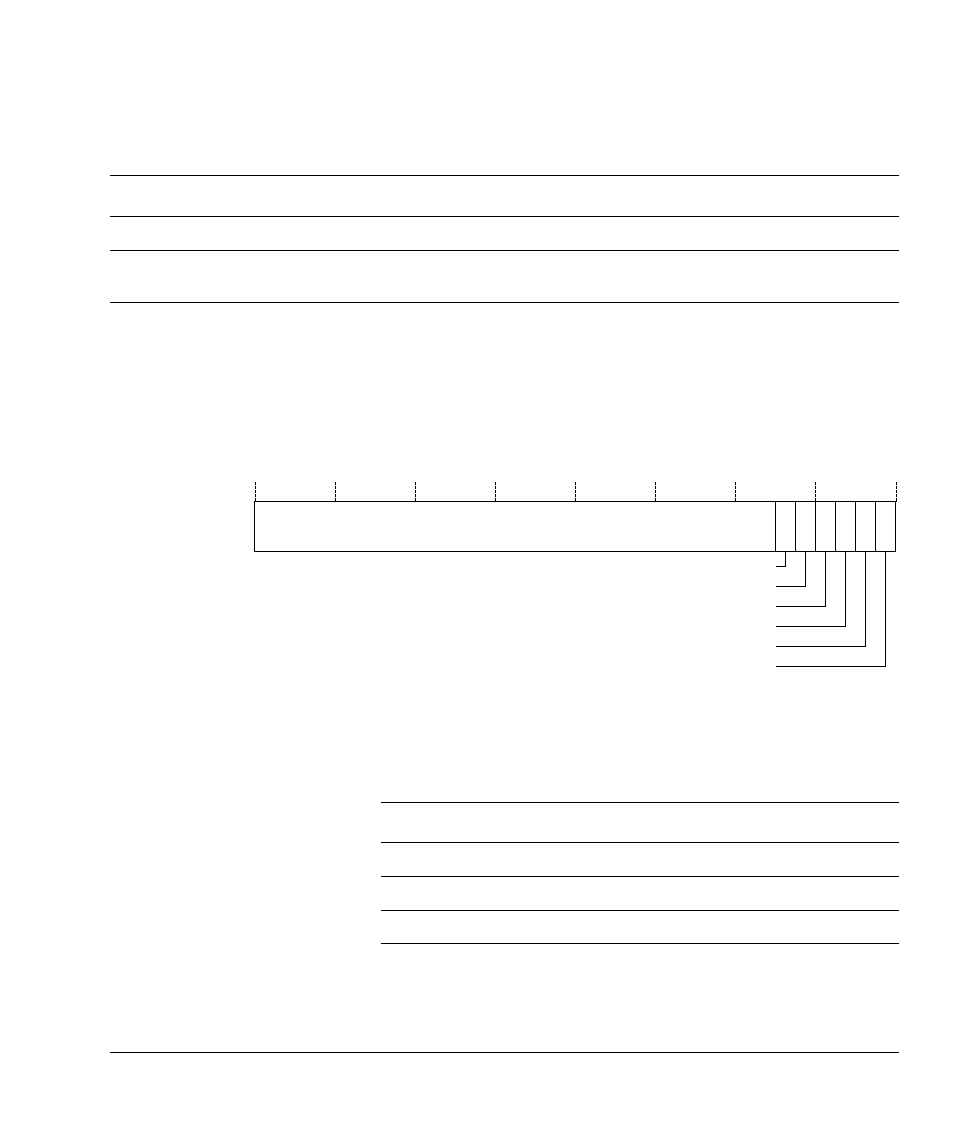

Figure 4-3 shows the register bit assignments.

Figure 4-3 smc_int_inputs Register bit assignments

Table 4-3 lists the register bit assignments.

Table 4-2 smc_int_cfg Register bit assignments

Bits

Name

Function

[31:1]

Undefined

Read undefined. Write as zero.

[0]

int_test_en

When set, outputs are driven from the integration test registers and tied-off, and inputs can change

for integration testing.

VPFBPV\QF

VPFBDV\QF

VPFBHELEDFNRII

VPFBHELJQW

VPFBFV\VUHT

8QGHILQHG

VPFBXVHBHEL

Table 4-3 smc_int_inputs Register bit assignments

Bits

Name

Function

[31:6]

-

Reserved, read undefined

[5]

smc_msync0

Returns the value of this top-level tie-off

[4]

smc_async0

Returns the value of this top-level tie-off

[3]

smc_ebibackoff0

Returns the value of the smc_ebibackoff0 input