Table 3-3, Smc_memif_cfg register bit assignments -7, Figure 3-7 – SMC Networks ARM PL241 User Manual

Page 67

Programmer’s Model

ARM DDI 0389B

Copyright © 2006 ARM Limited. All rights reserved.

3-7

3.3.2

SMC Memory Interface Configuration Register at 0x1004

The read-only smc_memif_cfg Register provides information on the configuration of

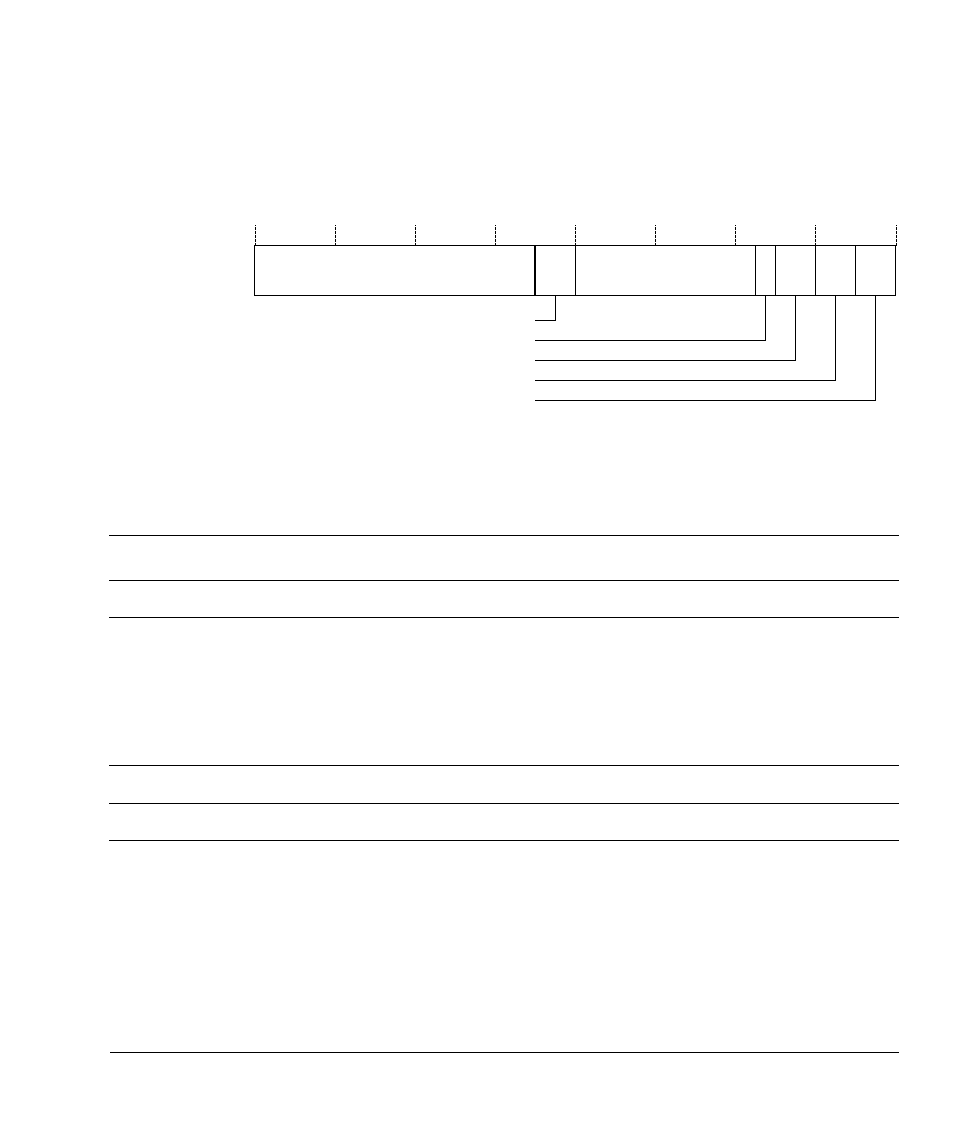

the memory interface. This register cannot be read in the Reset state. Figure 3-7 shows

the register bit assignments.

Figure 3-7 smc_memif_cfg Register bit assignments

Table 3-3 lists the register bit assignments.

PHPRU\BW\SH

PHPRU\BFKLSV

PHPRU\BZLGWK

UHPDS

H[FOXVLYHBPRQLWRUV

8QGHILQHG

5HVHUYHG

Table 3-3 smc_memif_cfg Register bit assignments

Bits

Name

Function

[31:18]

-

Reserved, read undefined.

[17:16]

exclusive_monitors

Returns the number of exclusive access monitor resources that are implemented in the

SMC:

b00 = 0 monitors

b01 = 1 monitors

b10 = 2 monitors

b11 = 4 monitors.

[15:7]

-

Reserved, read undefined.

[6]

remap0

Returns the value of the smc_remap0 input.

[5:4]

memory_width0

Returns the maximum width of the SMC memory data bus for interface 0:

b00 = 8 bits

b01 = 16 bits

b10 = 32 bits

b11 = Reserved.