Table 3-19, Smc_pcell_id register bit assignments -22, Figure 3-19 – SMC Networks ARM PL241 User Manual

Page 82

Programmer’s Model

3-22

Copyright © 2006 ARM Limited. All rights reserved.

ARM DDI 0389B

3.3.14

SMC PrimeCell Identification Registers <0-3> at 0x1FF0-0x1FFC

The smc_pcell_id Registers are four 8-bit wide registers, that span address locations

0xFF0-0FFC

. The registers can conceptually be treated as a single register that holds a

32-bit PrimeCell ID value. You can use the register for automatic BIOS configuration.

The smc_pcell_id Register is set to

0xB105F00D

. The register can be accessed with one

wait state. Table 3-19 lists the register bit assignments.

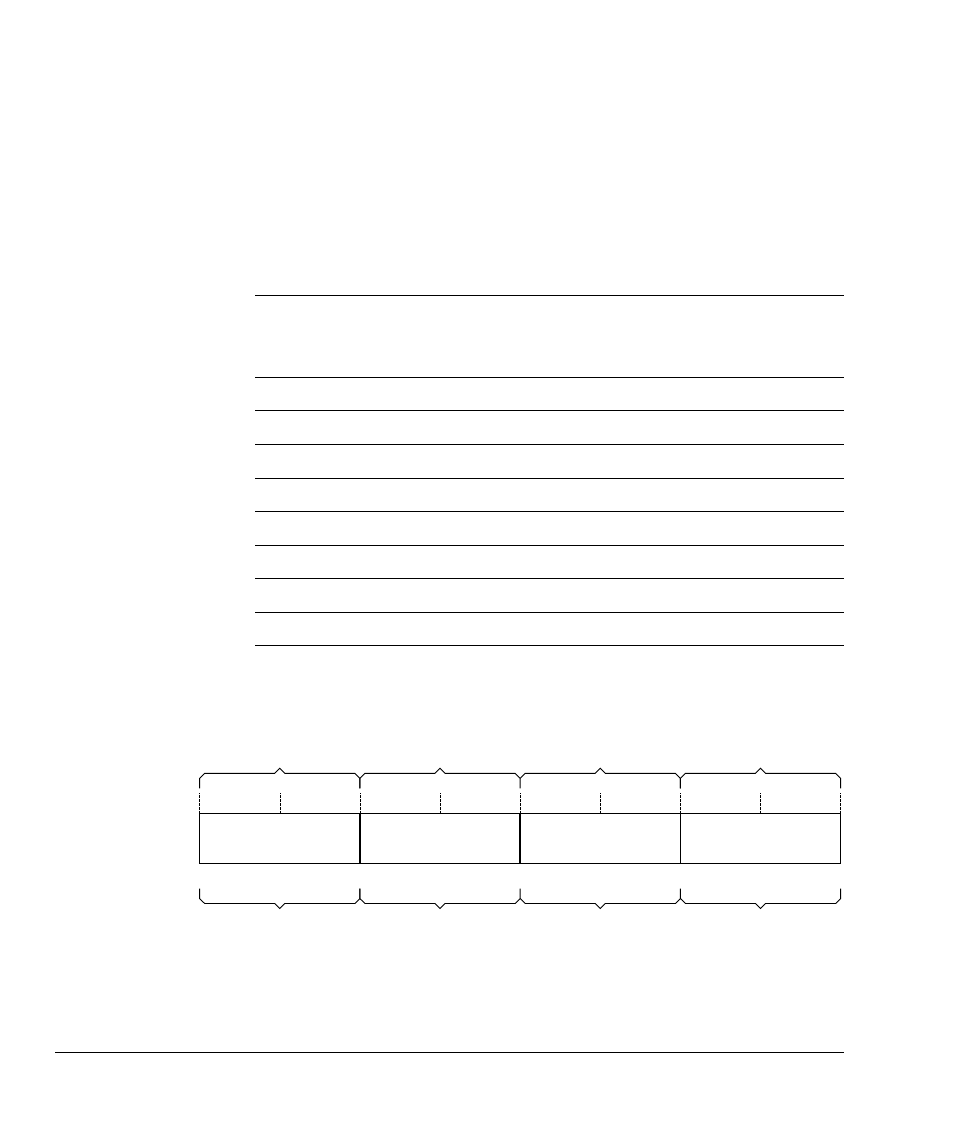

Figure 3-19 shows the register bit assignments.

Figure 3-19 smc_pcell_id Register bit assignments

Table 3-19 smc_pcell_id Register bit assignments

SMC pcell_id_0-3 register

Bits

Value

Register

Bits

Description

-

-

smc_pcell_id_3

[31:8]

Read undefined

[31:24]

0xB1

smc_pcell_id_3

[7:0]

These bits read back as

0xB1

-

-

smc_pcell_id_2

[31:8]

Read undefined

[23:16]

0x05

smc_pcell_id_2

[7:0]

These bits read back as

0x05

-

-

smc_pcell_id_1

[31:8]

Read undefined

[15:8]

0xF0

smc_pcell_id_1

[7:0]

These bits read back as

0xF0

-

-

smc_pcell_id_0

[31:8]

Read undefined

[7:0]

0x0D

smc_pcell_id_0

[7:0]

These bits read back as

0x0D

VPFBSFHOOBLGB

$FWXDOUHJLVWHUELWDVVLJQPHQW

&RQFHSWXDOUHJLVWHUELWDVVLJQPHQW

VPFBSFHOOBLGB

VPFBSFHOOBLGB

VPFBSFHOOBLGB

VPFBSFHOOBLGB

VPFBSFHOOBLGB

VPFBSFHOOBLGB

VPFBSFHOOBLGB